Datasheet DS 60S 219460 (F)

## **Product Summary**

The 4GB / 8GB Radiation Tolerant DDR4 Memory Multi-Chip Package (MCP) is a Ultra High Density Memory Solution, targeting Space Embedded Systems & Applications.

Such MCP products achieve significantly higher memory performance and density per cubic inch than using several discrete memories.

# **Top level Features**

Density 4GB / 8GB

• Bus width 72 bits (64 bits data + 8 bits ECC)

Speed Up to 2400 MT/s

Module size 15 mm x 20 mm x 1.92 mm

Solder Spheres Count 391

Pitch 0.8 mm

Mass 1.2g +/- 0.1g

### **Space Key Features**

## Space Qualification:

- Up to NASA Level 1 (based on NASA EEE-INST-002 Section M4 PEMs)

- o Up to ECSS Class 1 (ECSS-Q-ST-60-13C)

# Radiation Tolerance (for NASA and ECSS Flight Models):

Revision A (column "Rev" of the Ordering information standing for product revision):

- SEL LET Threshold > 60.88 MeV.cm²/mg

- o SEU evaluated from LET 2.6 MeV.cm²/mg & Upset cross-section @ 60.88 MeV.cm²/mg = 8.73E-12 cm²/bit

- SEFI evaluated from LET 2.6 MeV.cm²/mg & SEFI cross-section @ 60.88 MeV.cm²/mg = 4.17E-4 cm²/device

- TID tolerance: 100 krad(Si)

- Protons: Data is available up to 190MeV

Revision B (column "Rev" of the Ordering information standing for product revision)

- o SEL LET Threshold > 62.5 MeV.cm<sup>2</sup>/mg

- o SEU LET sensitivity Threshold: Under characterization

- o Logic error sensitivity Threshold: Under characterization

- o TID targeted tolerance: 100 krad(Si)

- o Protons: Data will be available up to 190MeV

# Low outgassing

- Compliant with ASTM 595 and ESCC-Q-ST-70-02 for Revision A ("Rev" column in Ordering Information)

- Under assessment for Revision B ("Rev" column in Ordering Information)

# **Revision History**

| Date | Revision | Description                                                                                                                                                                                                                                                    |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |          | Change radiation tolerance sentence Add X1 reference in Ordering information                                                                                                                                                                                   |

|      |          | Add note column on table 6 ball description                                                                                                                                                                                                                    |

| 2023 | F        | Add 7.5 DDR4 power consumption                                                                                                                                                                                                                                 |

| 2023 | E1       | "Proprietary and Confidential" removed                                                                                                                                                                                                                         |

| 2022 | E        | Update with 8GB information and ordering Information                                                                                                                                                                                                           |

| 2021 | D        | Add Capacitors note Add Outgassing feature Preliminary" removed Add Mass Add Differential Clock Termination scheme Add DDR4P and Grade notes in "Ordering Information" Add new references in "orderable parts" SEU LET sensitivity Theshold changed to 2.6 MeV |

| 2020 | С        | Temperature compensated refresh only operates on -40 to 105°C temperature range Update of mechanical outline and orderable parts list/table Add termination resistor value Correction of ball size from 0.5 to 0.4 mm                                          |

| 2020 | В        | Update of « Ordering Information » Add ball's information; Add orderable parts Change TID target to 100krad Add die configuration and notes Add Mass for RoHS parts Change PadOut picture Add Parity pin                                                       |

| 2020 | А        | Initial Baseline Release                                                                                                                                                                                                                                       |

# **Ordering Information**

| Product<br>Name     | Radiation<br>Performance | DDR<br>Size <sup>(2)</sup>     | Bus<br>width | Temperature<br>Range <sup>(2)</sup> | Package<br>Type <sup>(2)</sup>                                                                       | Speed<br>(MT/s) | Rev    | Grade <sup>(3)</sup>                                                                                                                                                                                          |

|---------------------|--------------------------|--------------------------------|--------------|-------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDR4 <sup>(1)</sup> | T : Rad Tol              | 04G : 4 GByte<br>08G : 8 GByte | 72 : 72 bits | M:-55/125C<br>A:-40/105C            | ZR: PBGA Stacked<br>Wire Bond (Leaded<br>SnPb)<br>ZS: PBGA Stacked<br>Wire Bond (Lead-<br>free RoHS) |                 | A<br>B | EM: Engineering Models  EQM: Engineering Qualification Models  -N1: Nasa Level 1  -N2: Nasa Level 2  -N3: Nasa Level 3  -E1: ECSS Class 1  -E2: ECSS Class 2  -E3: ECSS Class 3  -X1: Specific screening flow |

#### Notes:

- (1) "DDR4P" prototypes are functional devices dedicated to particular uses. Please contact Teledyne e2v sales office to know more about it

- (2) For availability of the different versions, contact Teledyne e2v sales office.

- (3) To know more about grades please refer to NE60S220869 on our website (ne-60s-220869-b0.pdf (teledyneimaging.com)

#### **Orderable Parts**

## Available EM:

DDR4T04G72AZR1AEM (4GB - [-40/105°C] - Leaded SnPb - 2133MT/s) DDR4T04G72AZR2AEM (4GB - [-40/105°C] - Leaded SnPb - 2400MT/s)

#### Available EQM, FM or X1:

DDR4T04G72AZR1AXXX\* (4GB - [-40/105°C] - Leaded SnPb-2133MT/s) DDR4T04G72AZR2AXXX\* (4GB - [-40/105°C] - Leaded SnPb-2400MT/s)

DDR4T04G72MZR1AXXX\* (4GB - [-55/125°C] - Leaded SnPb-2133MT/s) DDR4T04G72MZR2AXXX\* (4GB - [-55/125°C] - Leaded SnPb-2400MT/s)

\*Note: "XXX" should be replaced by Grades: EQM, -N1, -N2, -N3, -E3, -X1

# **Table of Contents**

| 4                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                           |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1                                 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                           |

| 1.1                               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                           |

| 1.2                               | Benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                           |

| 1.3                               | Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                       | R                           |

| 1.5                               | 1.3.1 Data Sheet Information                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |

|                                   | 1.3.2 Design Guide                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

| 1.4                               | Mapping of MCP signals to JEDEC DDR4 288pin UDIMM & DDR4 260 pin SO-DIMM signal                                                                                                                                                                                                                                                                                                                                                                             | als10                       |

| 1.5                               | DDR4 SPEED BINs and Timing Summary                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                          |

| 1.6                               | Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                          |

| 2                                 | DDR4 MCP BALL ASSIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                          |

| 2.1                               | MCP Data Byte Ball Assignments (4GB/8GB)                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                          |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

| 3                                 | BALL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                          |

| 4                                 | MECHANICAL OUTLINE - PACKAGE DETAILS                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                          |

| 5                                 | DDR4 MODE REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                          |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

| 5.1                               | Programming Mode Registers                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                          |

| 5.1                               | Programming Mode Registers                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>15</b>                   |

| 5.1                               | Programming Mode Registers                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                          |

| <ul><li>5.1</li><li>5.2</li></ul> | 5.1.1 tMRD Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>16                    |

|                                   | 5.1.1 tMRD Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>16<br><b>16</b><br>18 |

|                                   | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency                                                                                                                                                                                                                                                                                                                                 |                             |

|                                   | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode                                                                                                                                                                                                                                                                                                                 |                             |

|                                   | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency                                                                                                                                                                                                                                                                                                                                 |                             |

|                                   | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0                                                                                                                                                                                                                                                                                                                                                                                        |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET                                                                                                                                                                                                                                                      |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1  5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values                                                                                                                                       |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1  5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency                                                                                                                |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1  5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency 5.3.5 Write Leveling                                                                                           |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1  5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency                                                                                                                |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0  5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1  5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency 5.3.5 Write Leveling 5.3.6 Output Disable 5.3.7 Termination Data Strobe                                        |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0 5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1 5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency 5.3.5 Write Leveling 5.3.6 Output Disable 5.3.7 Termination Data Strobe  MODE REGISTER 2                         |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0 5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1 5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency 5.3.5 Write Leveling 5.3.6 Output Disable 5.3.7 Termination Data Strobe  MODE REGISTER 2 5.4.1 CAS WRITE Latency |                             |

| 5.2                               | 5.1.1 tMRD Timing Diagram 5.1.2 tMOD Timing Diagram  MODE REGISTER 0 5.2.1 Burst Length, Type, and Order 5.2.2 CAS Latency 5.2.3 Test Mode 5.2.4 Write Recovery(WR)/READ-to-PRECHARGE 5.2.5 DLL RESET  MODE REGISTER 1 5.3.1 DLL Enable/DLL Disable 5.3.2 Output Driver Impedance Control 5.3.3 ODT RTT(NOM) Values 5.3.4 Additive Latency 5.3.5 Write Leveling 5.3.6 Output Disable 5.3.7 Termination Data Strobe  MODE REGISTER 2 5.4.1 CAS WRITE Latency |                             |

|     | 5.4.5       | Target Row Refresh Mode                      | 26  |

|-----|-------------|----------------------------------------------|-----|

| 5.5 | MODE        | REGISTER 3                                   |     |

|     | 5.5.1       | Multipurpose Register                        | 28  |

|     | 5.5.2       | WRITE Command Latency When CRC/DM is Enabled | 28  |

|     | 5.5.3       | Fine Granularity Refresh Mode                |     |

|     | 5.5.4       | Temperature Sensor Status                    |     |

|     | 5.5.5       | Per-DRAM Addressability                      |     |

|     | 5.5.6       | Gear-Down Mode                               |     |

| 5.6 | MODE        | REGISTER 4                                   | 29  |

|     | 5.6.1       | Post Package Repair Mode                     |     |

|     | 5.6.2       | Soft Post Package Repair Mode                |     |

|     | 5.6.3       | WRITE Preamble                               |     |

|     | 5.6.4       | READ Preamble                                |     |

|     | 5.6.5       | READ Preamble Training                       |     |

|     | 5.6.6       | Temperature-Controlled Refresh               |     |

|     |             |                                              |     |

|     | 5.6.7       | Command Address Latency                      |     |

|     | 5.6.8       | Internal VREF Monitor                        |     |

|     | 5.6.9       | Maximum Power Savings Mode                   | 31  |

| 5.7 | MODE        | REGISTER 5                                   |     |

|     | 5.7.1       | Data Bus Inversion                           |     |

|     | 5.7.2       | Data Mask                                    | 34  |

|     | 5.7.3       | CA Parity Persistent Error Mode              | 34  |

|     | 5.7.4       | ODT Input Buffer for Power-Down              | 34  |

|     | 5.7.5       | CA Parity Error Status                       | 34  |

|     | 5.7.6       | CRC Error Status                             |     |

|     | 5.7.7       | CA Parity Latency Mode                       |     |

| 5.8 | MODE        | REGISTER 6                                   | 35  |

|     | 5.8.1       | t <sub>CCD L</sub> Programming               |     |

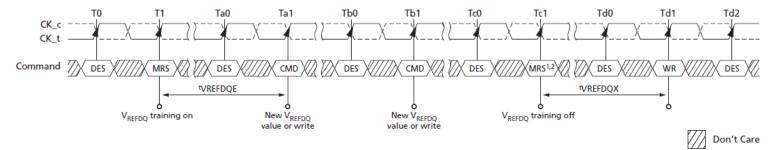

|     | 5.8.2       | VREFDQ Calibration Enable                    |     |

|     | 5.8.3       | VREFDQ Calibration Range                     |     |

|     | 5.8.4       | VREFDQ Calibration Value                     |     |

|     |             |                                              |     |

| 6   | DQ IN       | ITERNAL VREF SPECIFICATIONS                  | 37  |

| 6.1 | VREF        | DQ Calibration and Training                  | 37  |

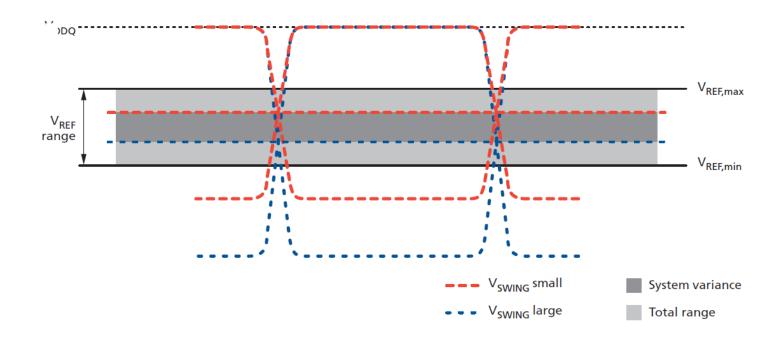

|     | 6.1.1       | VREFDQ Voltage Range                         |     |

|     | 6.1.2       | VREFDQ Range and Levels                      |     |

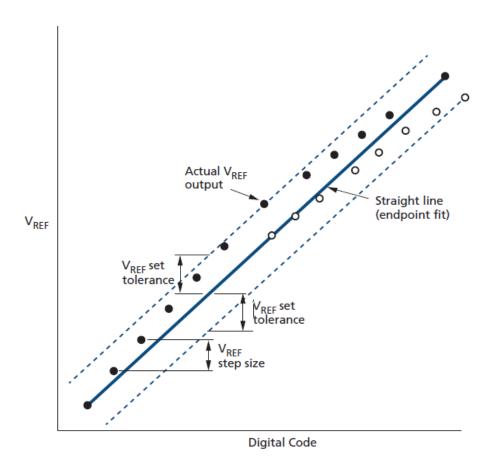

|     | 6.1.3       | VREFDQ Step Size                             | 39  |

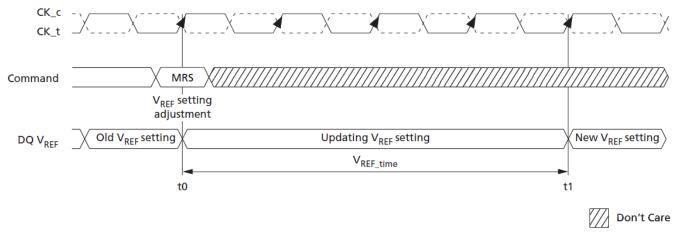

|     | 6.1.4       | VREFDQ Increment and Decrement Timing        |     |

|     | 6.1.5       | VREFDQ Target Settings                       |     |

| _   | <b>DO 0</b> | DED ATIMO COMPITIONO AND CHARACTERISTICS     | 40  |

| 7   | DC O        | PERATING CONDITIONS AND CHARACTERISTICS      | 46  |

| 7.1 | ABSO        | LUTE MAXIMUM RATINGS                         | 46  |

| 7.2 | MCP (       | Component Operating Temperature Range        | 46  |

| 7 2 | 4DEE!       | by Temperature                               | 4-7 |

| 7.3 | IKEFI       | by remperature                               | 47  |

| 7.4 | DC OF       | PERATING VOLTAGE                             | 47  |

| 7.5 | DDR4        | power consumption                            | 47  |

| 8   | AC OPERATING CONDITIONS AND CHARACTERISTICS | .49  |

|-----|---------------------------------------------|------|

| 8.1 | Speed Bins by Speed Grade                   | . 49 |

# 1 Introduction

The 4GB / 8GB Radiation Tolerant DDR4 Memory Multi-Chip Package (MCP) is a Ultra High Density Memory Solution, targeting Space Systems & Applications.

Such MCP products achieve significantly higher memory performance and density per cubic inch than using multiple discrete memories.

#### 1.1 Features

- JEDEC Standard Power Supply

- $\circ$  VDD = 1.2V ± 5% (VDDQ is not used)

- External VPP = 2.5 Volt +10%, -5%

- 391 ball MCP

- Die configuration<sup>(1)</sup>:

- o 4GB parts are based on x16 die configuration (2)

- o 8GB parts are based on x8 die configuration

- 1.2V Pseudo-open drain I/O (POD12) DQ lines

- Internally generated VrefDQ

- ECC recovery from command and parity errors

- Programmable CAS Latency: 13,15,16,17,19

- Programmable CAS Write Latency (CWL).

- Programmable Additive Latency (Posted CAS)

- Per DRAM addressability is supported

- Data Bus Inversion support for x8 and x16 devices

- Command/Address (CA) Parity

- On-chip CA Parity detection for the CA bus

- Databus write cyclic redundancy check (CRC)

- Output Driver Calibration

- Reduced interconnect routing

- Reduced trace lengths due to the highly integrated, impedance matched packaging

- Thermally enhanced packaging technology allows silicon integration without performance degradation due to power dissipation (heat)

- Selectable Fixed burst chop of 4 (BC4) and burst length of 8 (BL8) on-the-fly (OTF) via the mode register set (MRS)

- 8n prefetch with 2 bank groups: 8 banks (2 bank groups x 4 banks per bank group)

- Separate activation, read, write, refresh operations for each bank group

- 7 mode registers

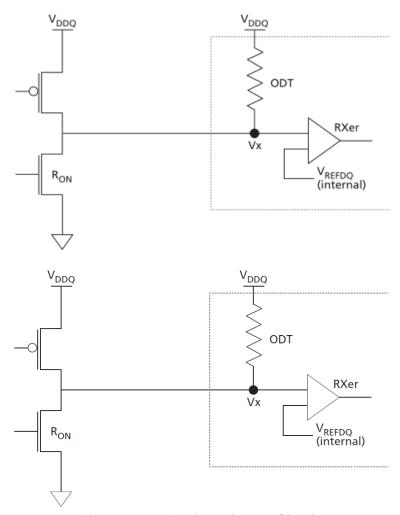

- Dynamic On-Die-Termination (ODT) and ODT Park for improved signal integrity.

- Self Refresh, Self Refresh abort and several Power Down Modes

- DLL-off mode for power savings

- System Level Timing Calibration Support via Write Leveling and Multi Purpose Register (MPR) Read Pattern

- Asynchronous Reset

- Bidirectional Differentially Buffered Data Strobes

- SnPb and RoHS Compliant package available

- Temperature Compensated Refresh for operating temperature: Extended -40 to 105°C

#### Notes:

Refer to 'table 2' for more details on the differences between 4GB and 8GB devices ECC uses only the lower byte of the x16 die, the upper byte is not connected

## 1.2 Benefits

- Very small footprint: saves board space versus implementation with discrete components

- Very high memory capacity per cubic inch

- Very high memory bandwidth per cubic inch

- Rugged: soldered-down PBGA

- Superior signal integrity

- 0.8 mm pitch: leadfree and leaded ball options

- Suitability for use in High-Rel and Space applications requiring Mil-Temp range, small form factor, non-hermetic operation

# 1.3 Design Considerations

### 1.3.1 Data Sheet Information

- This product and/or its specifications are subject to change without notice.

- The latest data sheet document should be retrieved from Teledyne e2v, prior to your design consideration.

# 1.3.2 Design Guide

General design guidelines are provided in the following table. More details can be found in the general user guide of the memory (available on request)

Table 1: DDR4 Design Guide

| Item                                 | Description                                               | Implementation Suggestion                                                                                                                                                                  |

|--------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JEDEC                                | JEDEC Standards                                           | Follow guidelines per JEDEC Standards and Host Memory Interface requirements                                                                                                               |

| Placement                            | DDR4 Interface between MCP & Host / Memory Controller     | The MCP should be placed as close as possible to the processor/memory controller, with direct / straight interconnect between them.                                                        |

| Rtt Termination                      | Termination for DDR4 address/command/control signals      | Incorporated in MCP - not required externally The nominal value of the termination resistors is 69.8 ohms                                                                                  |

| Differential Clock<br>Termination    | Clock Termination for DDR differential clock input signal | Incorporated in MCP - not required externally  CK_t R1  36  C1  VDD  CK_c R2  10nF                                                                                                         |

| Decoupling                           | High Speed Decoupling                                     | The MCP incorporates some decoupling capacitors. For recommended external decoupling scheme please refer to the general user guide.                                                        |

| Bulk Decoupling                      | Low speed / low frequency                                 | Refer to general user guide                                                                                                                                                                |

| Plane                                | Power                                                     | Must incorporate Power Plane for good and effective power distribution                                                                                                                     |

| Plane                                | Ground                                                    | Must incorporate Ground Plane for good return path                                                                                                                                         |

| Thermal                              | Need to have extremely efficient heat dissipation paths   | Incorporate as many thermal relief vias as possible such as via in pad in Ground plane with copper fill or highly thermally conductive material fill                                       |

| Trace impedance                      | Impedance                                                 | Follow DDR4 impedance guidelines per signal group.                                                                                                                                         |

| Trace Spacing                        | Crosstalk                                                 | Traces shall be spaced such that crosstalk in minimized                                                                                                                                    |

| Trace Lengths                        | Data Byte Lanes                                           | Trace lengths for each Byte Lane shall be tuned to be within 1%                                                                                                                            |

| Trace Lengths                        | Address & Command                                         | Trace lengths for all Address and Control signals shall be tuned to be within 5%                                                                                                           |

| Calibration                          | Zq resistor for drive strength calibration                | Teledyne e2v recommends adding an external ZQ resistor population option to the motherboard layout (Zq=240 ohm +/- 1%).                                                                    |

| BG1 - 8GB capacity support           | Future migration to support 8GB capacity                  | BG1 should be routed to Host/Memory Controller for future migration to support 8GB capacity                                                                                                |

| Signal Integrity<br>Simulation       | End to End Simulation of all I/O signals                  | It is critical that simulation be done end to end from Host / Memory Controller to MCP package. Simulation should be done for each signal group i.e. Data, Address/Command, Control, Clock |

| Simulation Model                     | MCP Package, Die Models                                   | Spice model of the MCP package and IBIS model for the die as well as EBD model are available from Teledyne e2v                                                                             |

| Signal Integrity<br>Simulation Model | Host / Memory Controller                                  | Customer to use appropriate model for the Host / Memory Controller supplied by the respective manufacturer                                                                                 |

| Power consumption estimation         | Power calculation spreadsheet                             | This can be supplied by Teledyne e2V                                                                                                                                                       |

| Thermal<br>Simulation Model          | MCP thermal model                                         | This can be supplied by Teledyne e2v in Icepack or ECXML format                                                                                                                            |

# Table 2: Future Migration from 4GB to 8GB

| Signal       | Implementation                                                                                                                                                                                         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BG1          | To support future migration to 8GB part, this signal should be connected to the Host / Memory Controller.  All other signals are applicable for both capacities.  BG1 signal is not used in 4GB parts. |

| ZQ0 thru ZQ8 | Calibration Reference - To support future migration to 8GB part, connect all 9 ZQx signals to GND via 240Ω 1% Resistor and install them. ZQ1, ZQ3, ZQ5, ZQ7 signals are not used in 4GB parts.         |

# 1.4 Mapping of MCP signals to JEDEC DDR4 288pin UDIMM & DDR4 260 pin SO-DIMM signals.

For mapping of MCP signals to JEDEC DDR4 288pin UDIMM & DDR4 260 pin SO-DIMM signals, see Appendix A & B.

# 1.5 DDR4 SPEED BINs and Timing Summary

### **Table 3: DDR4 SPEED BIN Nomenclature**

| Speed     | Clock    |

|-----------|----------|

| DDR4-1866 | 933 MHz  |

| DDR4-2133 | 1066 MHz |

| DDR4-2400 | 1200 MHz |

# **Table 4: DDR4 Timing Summary**

| MT/s      | tCK (ns) | CAS Latency (tCK) | tRCD (ns) | tRP (ns) | tRAS (ns) | tRC (ns) | CL-tRCD-tRP |

|-----------|----------|-------------------|-----------|----------|-----------|----------|-------------|

| DDR4-1866 | 1.071    | 13                | 13.92     | 13.92    | 34        | 47.92    | 13-13-13    |

| DDR4-2133 | 0.93     | 15                | 14.06     | 14.06    | 33        | 47.05    | 15-15-15    |

| DDR4-2400 | 0.83     | 17                | 14.16     | 14.16    | 32        | 46.16    | 17-17-17    |

#### Notes

CL = CAS Latency, tRCD = Activate -to-Command Time, tRP = Precharge Time. Refer to Speed Bin tables for details.

# 1.6 Addressing

# Table 5: Addressing

|                      |                      | 4GB : 512Mx72            | 8GB : 1024Mx72            |  |

|----------------------|----------------------|--------------------------|---------------------------|--|

| Bank Address         | # of Bank Groups     | 2                        | 4                         |  |

|                      | BG Address           | BG0                      | BG0,BG1                   |  |

|                      | Bank Address in a BG | BA0 to BA1               | BA0 to BA1                |  |

| Bank Count per Group |                      | 4                        | 4                         |  |

| Row Address          |                      | 64K(A0 to A15)           | 64K(A0 to A15)            |  |

| Column Address       |                      | 1K(A0 to A9)             | 1K(A0 to A9)              |  |

| Die Organization     |                      | 8Gb (512M x 16), 8 Banks | 8Gb (1024M x 8), 16 Banks |  |

| MCP Rank Address     |                      | CS0_n                    | CS0_n                     |  |

# 2 DDR4 MCP Ball Assignments

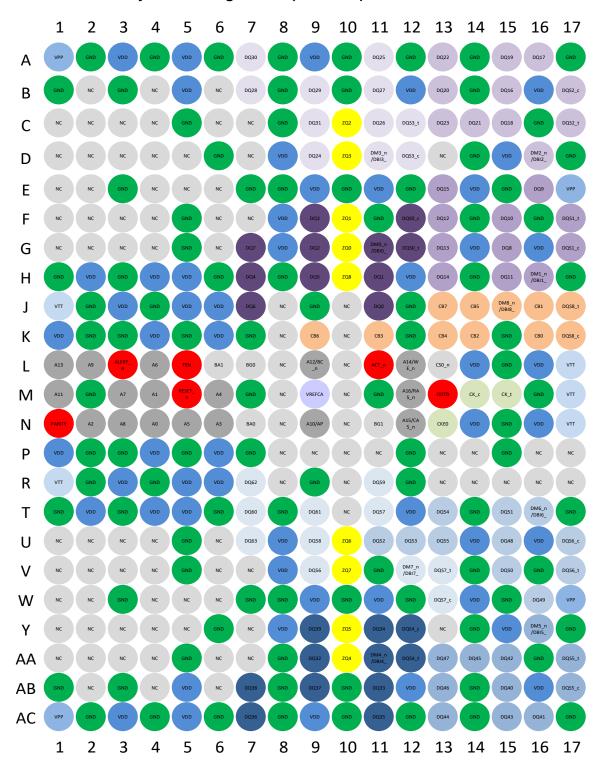

# 2.1 MCP Data Byte Ball Assignments (4GB/8GB)

DataByte 0 DataByte 0 DataByte 1 DataByte 2 DataByte 3 DataByte 4 DataByte 5 DataByte 6 DataByte 7 **ECC** Byte Clock Address Bank Group Miscellaneous Ground / VSS **VREFCA** VDD VPP VTT ZQ TEN

No Connect

Top view, A1 top left corner

# 3 Ball Description

Number of solder balls: 391

• Ball diameter: 0.4 mm

Pitch: 0.80 mm

Solder balls for leaded option: 63%Sn, 37%Pb

• Solder balls for Lead-free RoHS option: 96.5%Sn, 3%Ag, 0.5%Cu

# **Table 6: Ball Description**

| Symbol                                                      | Туре             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note |

|-------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CK_t, CK_c                                                  | Input            | Clock: CK_t and CK_c are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| CKE0                                                        | Input            | Clock Enable: CKE0 HIGH activates, and CKE0 Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE0 Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE0 is asynchronous for Self-Refresh exit. After VREFCA and VREFDQ have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK_c, ODT and CKE0, are disabled during power-down. Input buffers, excluding CKE0, are disabled during Self-Refresh. | 1    |

| CS0_n                                                       | Input            | Chip Select: All commands are masked when CS0_n is registered HIGH. CS0_n provides for external Rank selection on systems with multiple Ranks. CS0_n is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1    |

| ODT0                                                        | Input            | On Die Termination: ODT0 (registered HIGH) enables termination resistance internal to the DDR4 SDRAM. When enabled, ODT0 is only applied to each DQ, DQS_t, DQS_c and DM_n/DBI_n/TDQS_t,NU/TDQS_c (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 configurations. For x16 configuration ODT0 is applied to each DQ, DQSU_c, DQSU_t, DQSL_t, DQSL_c, DMU_n, and DML_n signal. The ODT0 ball will be ignored if MR1 is programmed to disable RTT_NOM.                                                                                                                                                                                                                                      | 1    |

| PARITY                                                      | Input            | Parity for command and address: This function can be enabled or disabled via the mode register. When enabled, the parity signal covers all command and address inputs, including ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, A[17;0], A10/AP, A12/BC_n, BA[1;0] and BG[1;0] with C0, C1 and C2 on 3DS only devices. Control pins NOT covered by the parity signal are CS_n, CKE, and ODT. Unused address pins that are density and configuration specific should be treated internally as 0s by the DRAM pariy logic. Command and address inputs will have parity check performed when commands are latched via the rising edge of CK_t and when CS_n is LOW.                                                     | 1    |

| ACT_n                                                       | Input            | Activation Command Input: ACT_n defines the Activation command being entered along with CS0_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be considered as Row Address A16, A15 and A14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1    |

| RAS_n/A16,<br>CAS_n/A15,<br>WE_n/A14                        | Input            | Command Inputs RAS_n/A16, CAS_n/A15 and WE_n/A14 (along with CS0_n) define the command being entered. Those balls have multi function. For example, for activation with ACT_n Low, those are Addressing like A16,A15 and A14 but for non-activation command with ACT_n High, those are Command balls for Read, Write and other command defined in command truth table.                                                                                                                                                                                                                                                                                                                                       | 1    |

| DM_n/DBI_n/<br>TDQS_t,<br>(DMU_n/DBIU_n),<br>(DML_n/DBIL_n) | Input/<br>Output | Input Data Mask and Data Bus Inversion: DM_n is an input mask signal for write data. Input data is masked when DM_n is sampled LOW coincident with that input data during a Write access. DM_n is sampled on both edges of DQS. DM is muxed with DBI function by Mode Register A10,A11,A12 setting in MR5. For x8 device, the function of DM or TDQS is enabled by Mode Register A11 setting in MR1. DBI_n is an input/output identifying whether to store/output the true or inverted data. If DBI_n is LOW, the data will be stored/output after inversion inside the DDR4 SDRAM and not inverted if DBI_n is HIGH. TDQS is only supported in x8.                                                          |      |

| BG0 - BG1                                                   | Input            | Bank Group Inputs: BG0 - BG1 define to which bank group an Active, Read, Write or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle. x4/8 have BG0 and BG1 but x16 has only BG0.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1    |

| BA0 - BA1                                                   | Input            | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1    |

| Symbol                                                | Туре              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Note |

|-------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A0-A13, A17                                           | Input             | Address Inputs: Provided the row address for ACTIVATE Commands and the column address for Read/Write commands th select one location out of the memory array in the respective bank. (A10/AP, A12/BC_n, RAS_n/A16, CAS_n/A15 and WE_n/A14 have additional functions, see other rows. The address inputs also provide the op-code during Mode Register Set commands. A17 is only defined for the x4 configuration.                                                                                         | 1    |

| A10 / AP                                              | Input             | Auto-precharge: A10 is sampled during Read/Write commands to determine whether Autoprecharge should be performed to the accessed bank after the Read/Write operation. (HIGH: Autoprecharge; LOW: no Autoprecharge).A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                      |      |

| A12 / BC_n                                            | Input             | Burst Chop: A12 / BC_n is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                               |      |

| RESET_n                                               | Input             | Active Low Asynchronous Reset: Reset is active when RESET_n is LOW, and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation. RESET_n is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD.                                                                                                                                                                                                                                                                    |      |

| DQ<63:00>                                             | Input /<br>Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0toDQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. Refer to vendor specific datasheets to determine which DQ is used.                                                                                                                                                                                         |      |

| CB<7:0>                                               | Input /<br>Output | Check Bit Input/ Output: Bi-directional ECC portion of data bus for x72 configurations                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| DQS_t, DQS_c,<br>DQSU_t,<br>DQSU_c,<br>DQSL_t, DQSL_c | Input /<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For x16, DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobe DQS_t, DQSL_t, and DQSU_t are paired with differential signals DQS_c, DQSL_c, and DQSU_c, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended. |      |

| ALERT_n                                               | Output            | Alert: It has multi functions such as CRC error flag, Command and Address Parity error flag. If there is error in CRC, then Alert_n goes LOW for the period time interval and goes back HIGH. IF there is error in Command Address Parity Check, then Alert_n goes LOW for relatively long period until on going DRAM internal recovery transaction to complete.  This signal is internally pulled-up to VDD with a 51Ω resistor. No external resistor is required.                                       |      |

| TEN                                                   | Input             | Boundary Scan Mode Enable: Required on x16 devices and optional input on x4/x8 with densities equal to or greater than 8Gb. HIGH in this ball will enable boundary scan operation along with other balls. It is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD.                                                                                                                                                                                                                    |      |

| NC                                                    |                   | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| VDD                                                   | Supply            | Power Supply: 1.2 V +/- 0.06 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| GND                                                   | Supply            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| VTT                                                   | Supply            | Power Supply: 0.6 V +/- 3%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Vpp                                                   | Supply            | DRAM Activation Power Supply: 2.5V (2.375V min , 2.75 max)                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| VREFCA                                                | Supply            | Reference voltage for CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| ZQ                                                    | Supply            | Reference Ball for ZQ calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

Note:

<sup>1)</sup> No external termination required on input only balls

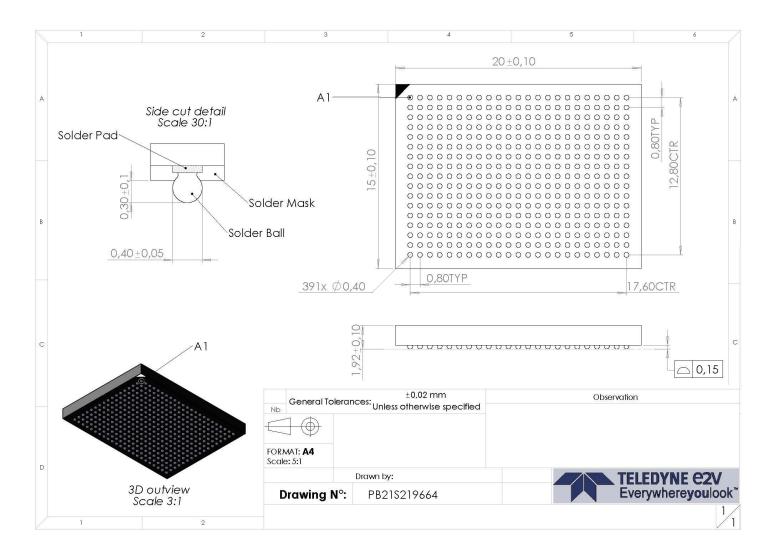

# 4 MECHANICAL OUTLINE - PACKAGE DETAILS

Figure 1. MECHANICAL OUTLINE - PACKAGE DETAILS

# 5 DDR4 MODE REGISTERS

# 5.1 Programming Mode Registers

For application flexibility, various functions, features, and modes are programmable in seven mode registers (MR n) provided by the device as user defined variables that must be programmed via a MODE REGISTER SET (MRS) command. Because the default values of the mode registers are not defined, contents of mode registers must be fully initialized and/or re-initialized; that is, they must be written after power-up and/or reset for proper operation. The contents of the mode registers can be altered by re-executing the MRS command during normal operation. When programming the mode registers, even if the user chooses to modify only a sub-set of the MRS fields, all address fields within the accessed mode register must be redefined when the MRS command is issued. MRS and DLL RESET commands do not affect array contents, which means these commands can be executed any time after power-up without affecting the array contents. The MRS command cycle time, tMRD, is required to complete the WRITE operation to the mode register and is the minimum time required between the two MRS commands shown in the tMRD Timing figure. Some of the mode register settings affect address/command/control input functionality. In these cases, the next MRS command can be allowed when the function being updated by the current MRS command is completed. These MRS commands don't apply tMRD timing to the next MRS command; however, the input cases have unique MR setting procedures, so refer to individual function descriptions:

- Gear-down mode

- Per-DRAM addressability

- Maximum power saving mode

- CS to command/address latency

- CA parity latency mode

- VREFDQ training value

- VREFDQ training mode

- VREFDQ training range

Some mode register settings may not be supported because they are not required by certain speed bins.

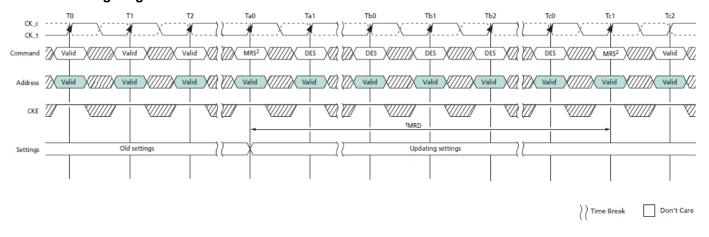

# 5.1.1 tMRD Timing Diagram

Figure 2. tMRD Timing

#### Notes:

This timing diagram depicts CA parity mode "disabled" case. tMRD applies to all MRS commands with the following exceptions: Gear-down mode CA parity mode CAL mode

Per-DRAM addressability mode

VREFDQ training value, VREFDQ training mode, and VREFDQ training range

The MRS command to nonMRS command delay, tMOD, is required for the DRAM to update features, except DLL RESET. tMOD is the minimum time required from an MRS command to a nonMRS command, excluding DES, as shown in the tMOD Timing figure.

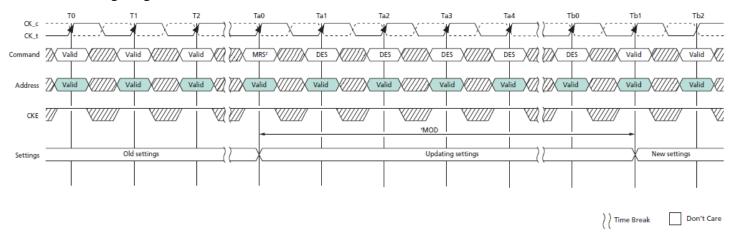

## 5.1.2 tMOD Timing Diagram

Figure 3. tMOD Timing

#### Notes

This timing diagram depicts CA parity mode "disabled" case.

tMOD applies to all MRS commands with the following exceptions:

DLL enable, Gear-down mode

VREFDQ training value, internal VREF training monitor, VREFDQ training mode, and VREFDQ training range Maximum power savings mode , Per-DRAM addressability mode, and CA parity mode

The mode register contents can be changed using the same command and timing requirements during normal operation as long as the device is in idle state; that is, all banks are in the precharged state with tRP satisfied, all data bursts are completed, and CKE is HIGH prior to writing into the mode register. If the RTT(NOM) feature is enabled in the mode register prior to and/or after an MRS command, the ODT signal must continuously be registered LOW, ensuring RTT is in an off state prior to the MRS command. The ODT signal may be registered HIGH after tMOD has expired. If the RTT(NOM) feature is disabled in the mode register prior to and after an MRS command, the ODT signal can be registered either LOW or HIGH before, during, and after the MRS command. The mode registers are divided into various fields depending on functionality and modes. In some mode register setting cases, function updating takes longer than tMOD. This type of MRS does not apply tMOD timing to the next valid command, excluding DES. These MRS command input cases have unique MR setting procedures, so refer to individual function descriptions.

# 5.2 MODE REGISTER 0

Mode register 0 (MR0) controls various device operating modes as shown in the following register definition table. Not all settings listed may be available on a die; only settings required for speed bin support are available. MR0 is written by issuing the MRS command while controlling the states of the BGx, BAx, and Ax address pins. The mapping of address pins during the MRS command is shown in the following MR0 Register Definition table.

**Table 7: Address Pin Mapping**

| Address Pin M | 1apping | l   |     |     |     |       |        |       |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

|---------------|---------|-----|-----|-----|-----|-------|--------|-------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Address bus   | BG1     | BG0 | BA1 | BA0 | A17 | RAS_n | CAS _n | WE _n | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

| Mode register | 21      | 20  | 19  | 18  | 17  | -     | -      | -     | 13  | 12  | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

**Note:** 1. RAS\_n, CAS\_n, and WE\_n must be LOW during MODE REGISTER SET command.

# **Table 8: MR0 Register Definition**

| Mode Register 0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21              | RFU 0 = Must be programmed to 0 1 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20:18           | MR select 000 = MR0 001 = MR1 010 = MR2 011 = MR3 100 = MR4 101 = MR5 110 = MR6 111 = DNU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17              | N/A on 4Gb and 8Gb, RFU 0 = Must be programmed to 0 1 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13,11:9         | WR (WRITE recovery)/RTP (READ-to-PRECHARGE)  0000 = 10 / 5 clocks1  0001 = 12 / 6 clocks  0010 = 14 / 7 clocks1  0011 = 16 / 8 / clocks  0100 = 18 / 9 clocks1  0101 = 20 / 10 clocks  0110 = 24 / 12 clocks  0111 = 22 / 11 clocks1  1000 = 26 / 13 clocks1  1001 through 1111 = Reserved                                                                                                                                                                                                                                                                                                           |

| 8               | DLL reset 0 = No 1 = Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7               | Test mode (TM) – Manufacturer use only 0 = Normal operating mode, must be programmed to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | CAS latency (CL) – Delay in clock cycles from the internal READ command to first data-out  00000 = 9 clocks1  00001 = 10 clocks  00010 = 11 clocks1  00011 = 12 clocks  00100 = 13 clocks1  00101 = 14 clocks  00110 = 15 clocks1  00111 = 16 clocks  10011 = 18 clocks  01000 = 18 clocks  01001 = 20 clocks  01001 = 20 clocks  01011 = 24 clocks  01101 = 22 clocks  01101 = 23 clocks1  01101 = 17 clocks1  01101 = 19 clocks1  01110 = 19 clocks1  01111 = 21 clocks 1  10000 = 25 clocks (3DS use only)  10001 = 27 clocks (3DS use only)  10011 = 28 clocks  10010 = 27 clocks (3DS use only) |

| 12, 6:4, 2      | 10011 = 28 Clocks<br>10100 = 29 clocks1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Mode Register 0 | Description                                                                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 10101 = 30 clocks<br>10110 = 31 clocks1<br>10111 = 32 clocks                                                                                                   |

| 3               | Burst type (BT) – Data burst ordering within a READ or WRITE burst access 0 = Nibble sequential 1 = Interleave                                                 |

| 1:0             | Burst length (BL) – Data burst size associated with each read or write access  00 = BL8 (fixed)  01 = BC4 or BL8 (on-the-fly)  10 = BC4 (fixed)  11 = Reserved |

**Note**: 1. Not allowed when 1/4 rate gear-down mode is enabled.

# 5.2.1 Burst Length, Type, and Order

Accesses within a given burst may be programmed to sequential or interleaved order. The ordering of accesses within a burst is determined by the burst length, burst type, and the starting column address as shown in the following table. Burst length options include fixed BC4, fixed BL8, and on-the-fly (OTF), which allows BC4 or BL8 to be selected coincidentally with the registration of a READ or WRITE command via A12/BC\_n.

Table 9: Burst Type and Burst Order

Note 1 applies to the entire table

| Burst<br>Length | READ/<br>WRITE | Starting Column Address (A[2, 1, 0]) | Burst Type = Sequential (Decimal) | Burst Type = Interleaved (Decimal) | Note<br>s |

|-----------------|----------------|--------------------------------------|-----------------------------------|------------------------------------|-----------|

| BC4             | READ           | 000                                  | 0, 1, 2, 3, T, T, T, T            | 0, 1, 2, 3, T, T, T, T             | 2, 3      |

|                 |                | 0 0 1                                | 1, 2, 3, 0, T, T, T, T            | 1, 0, 3, 2, T, T, T, T             | 2, 3      |

|                 |                | 010                                  | 2, 3, 0, 1, T, T, T, T            | 2, 3, 0, 1, T, T, T, T             | 2, 3      |

|                 |                | 011                                  | 3, 0, 1, 2, T, T, T, T            | 3, 2, 1, 0, T, T, T, T             | 2, 3      |

|                 |                | 100                                  | 4, 5, 6, 7, T, T, T, T            | 4, 5, 6, 7, T, T, T                | 2, 3      |

|                 |                | 101                                  | 5, 6, 7, 4, T, T, T, T            | 5, 4, 7, 6, T, T, T                | 2, 3      |

|                 |                | 110                                  | 6, 7, 4, 5, T, T, T, T            | 6, 7, 4, 5, T, T, T, T             | 2, 3      |

|                 |                | 111                                  | 7, 4, 5, 6, T, T, T, T            | 7, 6, 5, 4, T, T, T, T             | 2, 3      |

|                 | WRITE          | 0, V, V                              | 0, 1, 2, 3, X, X, X, X            | 0, 1, 2, 3, X, X, X, X             | 2, 3      |

|                 |                | 1, V, V                              | 4, 5, 6, 7, X, X, X, X            | 4, 5, 6, 7, X, X, X, X             | 2, 3      |

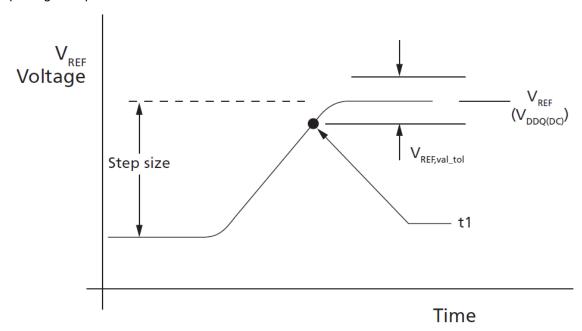

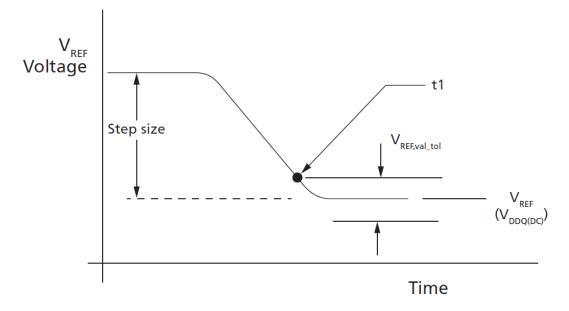

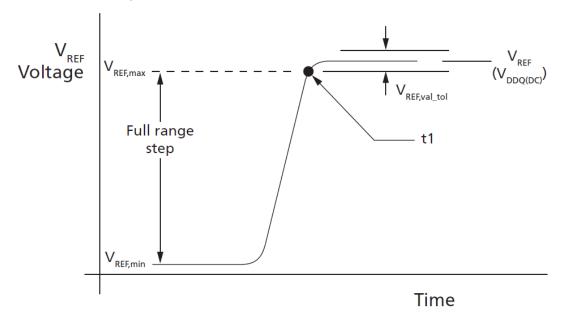

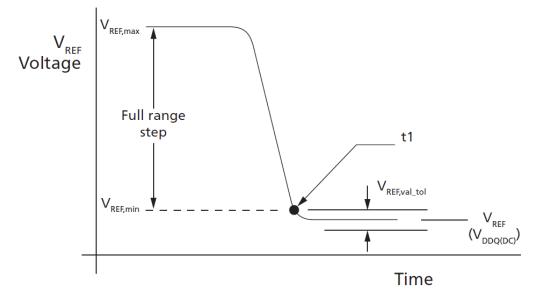

| BL8             | READ           | 000                                  | 0, 1, 2, 3, 4, 5, 6, 7            | 0, 1, 2, 3, 4, 5, 6, 7             |           |