# e2v

# EV10CS140 10-bit 3.0 Gsps 1:4 DMUX

# Datasheet

### **Main Features**

- High-speed ADC Family Companion Chip

- 10-bit Data

- Additional 11<sup>th</sup> Bit in Simultaneous Mode (Example: for Out-of-Range Bit)

- Staggered or Simultaneous Data Outputs

- Selectable 1:4 or 1:2 Demultiplexed Digital LVDS Outputs

- Power Consumption:

- 2.20 W in 1:4 DMUX Ratio

- 1.95 W in 1:2 DMUX Ratio

- Power Supplies:  $V_{CCD}$  = 3.3V (Digital),  $V_{PLUSD}$  = 2.5V (Outputs)

### **General Features**

- LVDS Compatible Differential Data and Clock Inputs (100 $\Omega$  Terminated)

- LVDS Compatible Differential Data and Data Ready Outputs

- Selectable Active Edge for Output Clocks:

- Only Rising: DR Mode

- Rising and Falling: DR/2 Mode

- Clock Input in CLK/2 Mode (Active on Rising and Falling Edge)

- Checker Board Data Frame Generator (BIST)

- Power Management (Sleep Mode)

- EBGA240 (Enhanced Ball Grid Array) Package

- Fine Tuning of Input Clock Path Delay

- Compensation of External Data and Clock Path Misalignements and Skews

- Once Tuned, Setting is Valid Over Full Operating Frequency and Over Specified Temperature Range

# Screening

- Temperature Range

- Industrial "V" Grade: -40°C < T<sub>amb</sub> < 85°C</li>

# Applications

This DMUX enables users to process high-speed output data streams from fast analog-to-digital converters down to standard FPGA processor speed.

### 1. Description

The EV10CS140 is a monolithic high speed-demultiplexer, used to lower a 10-bit data stream of up to 3 Gsps guaranteed rate by a selectable 4 or 2 ratio (a 1:8 ratio might be achieved by interleaving two DMUXes).

The DMUX is a companion chip designed to fit perfectly with all of e2v's high speed ADCs and is capable of tracking the ADC's output sampling rate over all operating frequency and temperature ranges.

Thanks to its LVDS buffers, this DMUX can easily be interfaced with standard high-speed FPGAs ( $100\Omega$  differentially terminated).

The EV10CS140 has the same pinout and footprint as e2v's AT84CS001 DMUX. No re-design efforts are required to use this low-power DMUX.

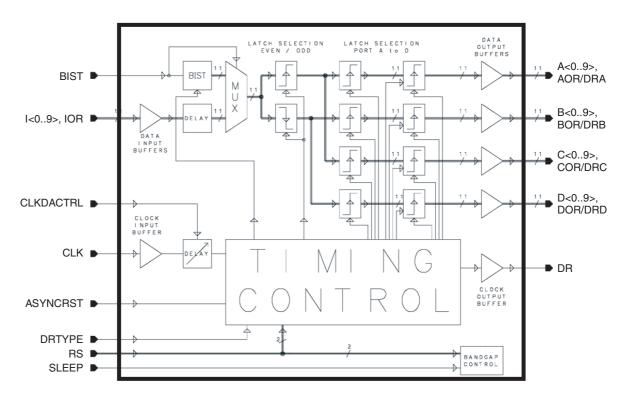

### 2. Functional Description

The EV10CS140 is a monolithic high-speed demultiplexer (DMUX) using high-speed bipolar technology.

It enables the user to lower a 10-bit stream of 3 Gsps minimum by a factor of two or four. The EV10CS140 DMUX can process an Input data rate up to 3Gsps in 1:4 ratio and 1:2 ratio.

The EV10CS140 DMUX is capable of processing an 11-bit data flow (in simultaneous mode). The additional 11<sup>th</sup> bit (IOR, IORN) might be connected for example to the out-of-range bit of a 10-bit ADC.

The input and output clocks as well as the input and output data are LVDS compatible. Digital inputs are  $100\Omega$  differentially terminated on chip. Digital output buffers shall be terminated by a  $100\Omega$  differential ASIC load.

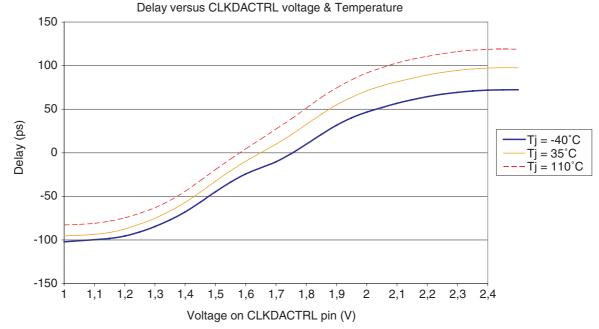

The improved architecture of the DMUX facilitates interfacing with high-speed ADCs operating at up to 3 Gsps. Over the full specified clock rate, it is normally not necessary to tune the CLKDACTRL voltage and it is recommended to bias CLKDACTRL pin with  $1/3^*V_{CCD}$  if the clock is roughly centered within input data. However, a tunable delay cell is integrated in serial with the clock input: it can be used to tune the delay between the data and clock paths namely for high speed rates and in the case of large misalignment or skews between the external clock path and the data path. The delay is controlled by means of the CLKDACTRL analog control input. The tunable delay ranges from -100 ps to 100 ps for CLK-DACTRL varying from  $1/3^*V_{CCD}$  to  $2/3^*V_{CCD}$ .

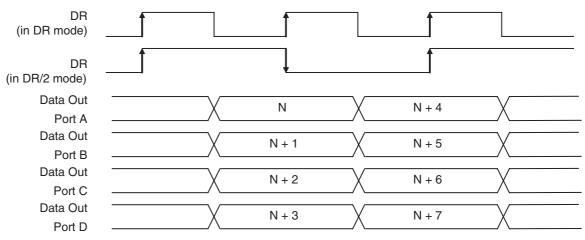

Two output Data Ready modes can be selected (DR and DR/2) by the means of DRTYPE control input:

- DR mode: only the output clock (DR, DRN) rising edges are active

- DR/2 mode: output clock (DR, DRN) rising and falling edges are active

The input clock has to be in CLK/2 mode (active on rising and falling edges)

The data outputs can be received at the DMUX output in two different modes:

- Staggered: even and odd bits are output with half a data period delay

- · Simultaneous: even and odd bits are output at the same time

The EV10CS140 DMUX is started by the ASYNCRST control input that acts as a master asynchronous reset for the device. Once reset, there is no loss of synchronization over an indefinite time period, therefore no additional incoming synchronous reset signal is required.

The power consumption of the EV10CS140 is 2.2W in 1:4 mode and 1.95W in 1:2 mode. Power consumption can be reduced at 1.0W by means of the SLEEP control input.

A Built-in Self Test (BIST) is implemented for rapid debugging of the DMUX.

The EV10CS140 DMUX is a companion chip designed to fit perfectly with all of e2v's high-speed ADCs.

Table 2-1.Functional Description

| Name                  | Function                                                                     |                               |                                     |                                        |

|-----------------------|------------------------------------------------------------------------------|-------------------------------|-------------------------------------|----------------------------------------|

| V <sub>CCD</sub>      | Digital 3.3V Power supply                                                    |                               |                                     |                                        |

| V <sub>PLUSD</sub>    | Output 2.5V Power Supply                                                     |                               |                                     |                                        |

| DGND                  | Ground                                                                       |                               |                                     |                                        |

| CLK, CLKN             | Input clock signals                                                          |                               |                                     |                                        |

| 1019                  | In-phase Input data (True)                                                   |                               |                                     |                                        |

| IONI9N                | Inverted phase Input data (False)                                            |                               |                                     |                                        |

| IOR, IORN             | Additional Input bit                                                         |                               |                                     |                                        |

| DR/DRN                | Output clock signals                                                         |                               |                                     |                                        |

| A0A9                  | In-phase Output data Port A                                                  |                               |                                     |                                        |

| A0NA9N                | Inverted phase Output data Port A                                            |                               |                                     |                                        |

| AOR/DRAN,<br>AORN/DRA | Additional Output bit Port A<br>Or Output clock in staggered mode for port A | [1019]                        | V <sub>CCD</sub> V <sub>PLUSD</sub> |                                        |

| B0B9                  | In-phase Output data Port B                                                  | [IONI9N]<br>[IOR, IORN] 22    |                                     | 20 [A0A9]<br>[A0NA9N]                  |

| B0NB9N                | Inverted phase Output data Port B                                            | CLK, CLKN                     |                                     | AOR/DRAN,<br>AORN/DRA<br>20 [B0B9]     |

| BOR/DRBN,<br>BORN/DRB | Additional Output bit Port B<br>Or Output clock in staggered mode for port B | ASYNCRST →                    |                                     | [B0NB9N]<br>2 BOR/DRBN,<br>20 [C0C9]   |

| C0C9                  | In-phase Output data Port C                                                  |                               | EV10CS140                           | 2 [C0NC9N]<br>COR/DRCN,<br>CORN/DRC    |

| C0NC9N                | Inverted phase Output data Port C                                            | SLEEP                         |                                     | 20 [D0D9]<br>2 [D0ND9N]<br>2 DOR/DRDN, |

| COR/DRCN,<br>CORN/DRC | Additional Output bit Port C<br>Or Output clock in staggered mode for port C | STAGG<br>RS<br>BIST<br>DRTYPE |                                     | 2 DORN/DRD<br>DR, DRN                  |

| D0D9                  | In-phase Output data Port D                                                  |                               |                                     |                                        |

| D0ND9N                | Inverted phase Output data Port D                                            |                               | DGND                                |                                        |

| DOR/DRDN,<br>DORN/DRD | Additional Output bit Port D<br>Or Output clock in staggered mode for port D |                               | DGIND                               |                                        |

| CLKDACTRL             | Control signal for Clock Delay cell                                          |                               |                                     |                                        |

| ASYNCRST              | Asynchronous Reset signal                                                    | _                             |                                     |                                        |

| SLEEP                 | Sleep mode selection signal                                                  |                               |                                     |                                        |

| RS                    | DMUX Ratio selection signal                                                  |                               |                                     |                                        |

| DRTYPE                | Output clock Type selection signal                                           |                               |                                     |                                        |

| STAGG                 | Staggered mode selection for Data outputs                                    |                               |                                     |                                        |

| BIST                  | Built-In Test enable                                                         |                               |                                     |                                        |

| DIODE                 | Diode for die Junction Temperature monitoring                                |                               |                                     |                                        |

Bit 0 corresponds to LSB and Bit 9 to MSB

### 3. Specifications

### 3.1 Absolute Maximum Ratings

Table 3-1.

Absolute Maximum Ratings

| Parameter                  | Symbol                                                 | Value                          | Unit |

|----------------------------|--------------------------------------------------------|--------------------------------|------|

| Digital power supply       | V <sub>CCD</sub>                                       | 3.6                            | V    |

| Output power supply        | V <sub>PLUSD</sub>                                     | 3.6                            | V    |

| Data Input                 | 10, 10N19, 19N, 10R, 10RN                              | -0.3 to V <sub>CCD</sub> + 0.3 | V    |

| Clock Input                | VCLK, VCLKN                                            | -0.3 to V <sub>CCD</sub> + 0.3 | V    |

| Control Inputs             | SLEEP, STAGG, RS, ASYNCRST,<br>BIST, DRTYPE, CLKDACTRL | -0.3 to V <sub>CCD</sub> + 0.3 | V    |

| Max Junction Temperature   | TJ                                                     | 125                            | °C   |

| Storage Temperature        | Tstg                                                   | -55 to 150                     | °C   |

| ESD protection (HBM model) | ESD                                                    | > 500                          | V    |

Notes: 1. Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability.

- 2. Maximum ratings on I/Os are defined with device powered ON.

- 3. All integrated circuits have to be handled with appropriate care to avoid damages due to ESD. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

### 3.2 Recommended Conditions of Use

| Table 3-2. Recommended Conditions of Use | Table 3-2. | Recommended Conditions of Use |

|------------------------------------------|------------|-------------------------------|

|------------------------------------------|------------|-------------------------------|

| Parameter                   | Symbol             | Comments                                     | Recommended                 | Unit |

|-----------------------------|--------------------|----------------------------------------------|-----------------------------|------|

| Digital power supply        | V <sub>CCD</sub>   | No specific power supply                     | 3.3                         | V    |

| Output power supply         | V <sub>PLUSD</sub> | sequencing required<br>during power ON / OFF | 2.5                         | V    |

| Control Inputs              | CLKDACTRL          |                                              | 1.1                         | V    |

| Operating Temperature Range | Тор                | Industrial grade                             | –40 < T <sub>amb</sub> < 85 | °C   |

### 3.3 Electrical Characteristics

Unless otherwise specified, the specification below apply over full temperature and power supply range.

**Table 3-3.**Electrical Characteristics

| Parameter                                                                                                                                   | Symbol                                                | Test Level | Min           | Тур                               | Мах                                                                                                        | Unit         |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------|---------------|-----------------------------------|------------------------------------------------------------------------------------------------------------|--------------|

| Resolution                                                                                                                                  |                                                       | 4          | 10 bit v      | vith additiona                    | l 11 <sup>th</sup> bit                                                                                     | Bit          |

| Power Requirements                                                                                                                          |                                                       |            |               |                                   |                                                                                                            |              |

| Digital power supply voltage                                                                                                                | V <sub>CCD</sub>                                      | 1          | 3.15          | 3.3                               | 3.45                                                                                                       | V            |

| Output power supply voltage                                                                                                                 | V <sub>PLUSD</sub>                                    | 1          | 2.375         | 2.5                               | 2.625                                                                                                      | V            |

| Digital power supply current<br>1:2 mode<br>1:4 mode<br>SLEEP mode (1:4 or 1:2)<br>1:2 mode with BIST enabled<br>1:4 mode with BIST enabled | I <sub>VCCD</sub>                                     | 1          |               | 385<br>440<br>135<br>360<br>415   | 450 <sup>(1)</sup><br>510 <sup>(1)</sup><br>170 <sup>(1)</sup><br>420 <sup>(1)</sup><br>480 <sup>(1)</sup> | mA           |

| Output power supply current<br>1:2 mode<br>1:4 mode<br>SLEEP mode (1:4 or 1:2)                                                              | I <sub>VPLUSD</sub>                                   | 1          |               | 270<br>300<br>240                 | 410 <sup>(1)</sup><br>440 <sup>(1)</sup><br>370 <sup>(1)</sup>                                             | mA           |

| Power dissipation<br>1:2 mode<br>1:4 mode<br>SLEEP mode (1:4 or 1:2)<br>1:2 mode with BIST enabled<br>1:4 mode with BIST enabled            | P <sub>D</sub>                                        | 1          |               | 1.95<br>2.2<br>1.1<br>1.85<br>2.1 | 2.6 <sup>(1)</sup><br>2.9 <sup>(1)</sup><br>1.5 <sup>(1)</sup><br>2.5 <sup>(1)</sup><br>2.8 <sup>(1)</sup> | w            |

| LVDS Data/Clock Inputs and Outputs                                                                                                          |                                                       | 1          | 1             |                                   |                                                                                                            | 1            |

| Logic Compatibility                                                                                                                         |                                                       |            |               | LVDS                              | 1                                                                                                          |              |

| Input Common Mode <sup>(2)</sup>                                                                                                            | V <sub>ICM</sub>                                      | 1          | 1             | 1.25                              | 1.6                                                                                                        | V            |

| Output Common Mode <sup>(3)</sup>                                                                                                           | V <sub>OCM</sub>                                      | 1          | 1.125         | 1.25                              | 1.425                                                                                                      | V            |

| Differential input <sup>(2)</sup>                                                                                                           | V <sub>IDIFF</sub>                                    | 1          | 100           | 350                               | -                                                                                                          | mV           |

| Differential output                                                                                                                         | V <sub>ODIFF</sub>                                    | 1          | 250           | 350                               | 450                                                                                                        | mV           |

| Output level "High" <sup>(4)</sup>                                                                                                          | V <sub>OH</sub>                                       | 1          | 1.25          | 1.425                             | -                                                                                                          | V            |

| Output level "Low" <sup>(4)</sup>                                                                                                           | V <sub>OL</sub>                                       | 1          | -             | 1.075                             | 1.25                                                                                                       | V            |

| STATIC Inputs (SLEEP, STAGG, BIST, R                                                                                                        | S, DRTYPE)                                            | 1          |               |                                   |                                                                                                            |              |

| Control Input Voltages and currents:<br>- Logic low                                                                                         |                                                       |            |               |                                   |                                                                                                            |              |

| Resistor to ground<br>Voltage level<br>Input low current                                                                                    | R <sub>IL</sub><br>V <sub>IL</sub><br>I <sub>IL</sub> | 1          | 0<br>0<br>500 |                                   | 10<br>0.5                                                                                                  | Ω<br>V<br>μΑ |

| - Logic high<br>Resistor to ground<br>Voltage level<br>Input high current                                                                   | R <sub>IH</sub><br>V <sub>IH</sub><br>I <sub>IH</sub> |            | 10k<br>2.0    |                                   | Infinite<br>V <sub>CCD</sub><br>10                                                                         | Ω<br>V<br>μΑ |

| STATIC Inputs (CLKDACTRL)                                                                                                                   |                                                       |            |               |                                   |                                                                                                            |              |

Unit

V

V µA

V µA

| <b>_</b>                                         | ·                                  |            |                      | _         |                        | r |

|--------------------------------------------------|------------------------------------|------------|----------------------|-----------|------------------------|---|

| Parameter                                        | Symbol                             | Test Level | Min                  | Тур       | Max                    | L |

| Control Input Voltages                           |                                    | 4          | V <sub>CCD</sub> / 3 |           | $2 \times V_{CCD} / 3$ |   |

| RESET Input (ASYNCRST)                           |                                    |            |                      |           |                        |   |

| Logic Compatibility                              |                                    |            | LV                   | /CMOS/CMC | S                      |   |

| Reset input voltages and currents<br>- Logic Low | V <sub>IL</sub><br>I <sub>IL</sub> | 1          | 0<br>-300            |           | 1.4                    |   |

| - Logic High                                     | V <sub>IH</sub><br>I <sub>IH</sub> |            | 1.8                  |           | V <sub>CCD</sub><br>50 |   |

#### Table 3-3. Electrical Characteristics (Continued)

Notes: 1. Worst case value obtained with maximum supply voltages over full temperature range.

- 2. Given for a differential input.

- 3. Assuming  $100\Omega$  termination ASIC load.

- 4.  $V_{OH}$  min and  $V_{OL}$  max can never be at 1.25V at the same time, with respect to  $V_{ODIFF}$  min = 250 mV

#### Table 3-4. Switching Performances and Characteristics

| Parameter                                                  | Symbol       | Test Level | Min  | Тур     | Max     | Unit |

|------------------------------------------------------------|--------------|------------|------|---------|---------|------|

| Input Clock                                                |              |            |      |         |         |      |

| Input Clock duty cycle                                     | DCYC         | 4          | 35   | 50      | 65      | %    |

| Maximum Input Clock Frequency                              |              |            |      |         |         |      |

| DR TYPE= DR/2, RS = 1:2                                    |              |            | 1.5  |         |         |      |

| DR TYPE= DR/2, RS = 1:4                                    | Fclk         | 4          | 1.5  |         |         | GHz  |

| DR TYPE= DR, RS = 1:2                                      |              |            | 1.5  |         |         |      |

| DR TYPE= DR, RS = 1:4                                      |              |            | 1.5  |         |         |      |

| Input Data                                                 |              |            |      |         |         |      |

| Data to Input Clock setup & hold time <sup>(1)</sup>       | Tsetup/THold | 4          |      |         |         | ps   |

| Maximum Input Data Rate                                    |              |            |      |         |         |      |

| DR TYPE= DR/2, RS = 1:2                                    |              |            | 3.0  |         |         |      |

| DR TYPE= DR/2, RS = 1:4                                    | Fs           | 4          | 3.0  |         |         | Gsps |

| DR TYPE= DR, RS = 1:2                                      |              |            | 3.0  |         |         |      |

| DR TYPE= DR, RS = 1:4                                      |              |            | 3.0  |         |         |      |

| Output Data                                                |              |            |      |         |         |      |

| Maximum Output Data Rate                                   |              |            |      |         |         |      |

| DR TYPE= DR/2, RS = 1:2                                    |              |            | 1.5  |         |         |      |

| DR TYPE= DR/2, RS = 1:4                                    |              | 4          | 0.75 |         |         | Gsps |

| DR TYPE= DR, RS = 1:2                                      |              |            | 1.5  |         |         |      |

| DR TYPE= DR, RS = 1:4                                      |              |            | 0.75 |         |         |      |

| Output Rise/Fall time for Data $(20\% - 80\%)^{(2)}$       | TR/TF        | 4          |      | 120/120 | 180/180 | ps   |

| Output Rise/Fall time for Data Ready $(20\% - 80\%)^{(2)}$ | TR/TF        | 4          |      | 120/120 | 180/180 | ps   |

| CLK to Data Output delay                                   | TOD          | 4          | 2.20 | 2.30    | 2.40    | ns   |

| CLK to Data Ready Output delay                             | TDR          | 4          | 2.10 | 2.15    | 2.20    | ns   |

| Data Ready to Data delay                                   | TOD – TDR    | 4          | 100  | 150     | 200     | ps   |

| Table 3-4. | Switching Performances and Characteristics (Continued) |

|------------|--------------------------------------------------------|

|------------|--------------------------------------------------------|

| Parameter                                                                                                                     | Symbol | Test Level | Min | Тур                                          | Мах  | Unit            |

|-------------------------------------------------------------------------------------------------------------------------------|--------|------------|-----|----------------------------------------------|------|-----------------|

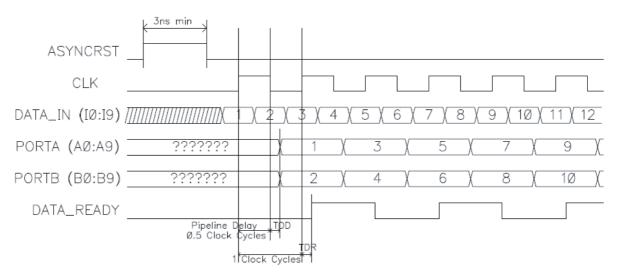

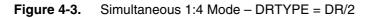

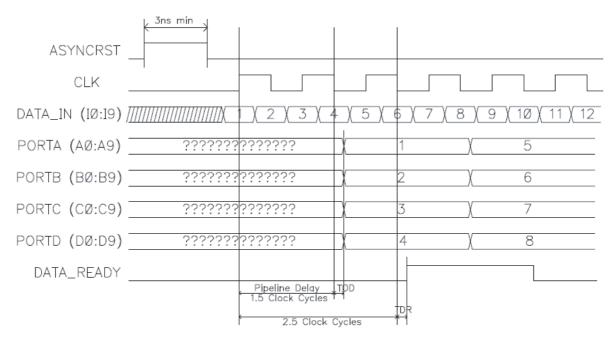

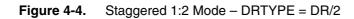

| Output Data Pipeline delay:<br>Synchronized 1:2 mode<br>Synchronized 1:4 mode                                                 | PD_D   | 4          |     | 0.5<br>1.5                                   |      | Clock           |

| Staggered 1:2 mode<br>Staggered 1:4 mode                                                                                      |        |            |     | 0 / 0.5<br>0 / 0.5 / 1 / 1.5                 |      | Cycles          |

| CLK to Output Data Ready delay:<br>Synchronized 1:2 mode<br>Synchronized 1:4 mode<br>Staggered 1:2 mode<br>Staggered 1:4 mode | PD_DR  | 4          |     | 1.0<br>2.5<br>0.5 / 1.0<br>1 / 1.5 / 2 / 2.5 |      | Clock<br>Cycles |

| Asynchronous Reset                                                                                                            |        |            |     |                                              |      |                 |

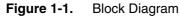

| ASYNCRST minimum pulse width                                                                                                  | RSTPW  | 5          |     | 3                                            |      | ns              |

| CLK to ASYNCRST timing <sup>(3)</sup><br>Forbidden area width                                                                 |        | 4          |     |                                              | 250  | ps              |

| Minimum delay between falling edge of ASYNCRST and rising edge of CLK                                                         |        | 4          |     |                                              | ±125 | ps              |

Notes: 1. Input data to input clock setup and hold time are not defined, because they are dependent of CLKDACTRL adjustment. It is recommended to center the clock edge in the middle of the data (with  $\pm$  100 ps) and to adjust CLKDACTRL to 1.1V (1/3 of V<sub>CCD</sub>).

2. Rise time and fall time are defined for an output load of 2 pF.

3. See Figure 4-1 on page 9, CLK to ASYNCRST timing is given assuming V(CLKDACTRL) = 1.1V

### 3.4 Explanation of Test Levels

Table 3-5. Test Levels

| 1 | 100% production tested at +25°C                                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------|

| 2 | 100% production tested at +25°C, and sample tested at specified temperature                                               |

| 3 | Sample tested only at specified temperature                                                                               |

| 4 | Parameter is guaranteed by design and characterization testing (thermal steady-state conditions at specified temperature) |

| 5 | Parameter is a typical value only                                                                                         |

Only MIN and MAX values are guaranteed (typical values are issuing from characterization results).

The level 1 and 2 tests are performed at 100 MHz

### 4. Timing Diagrams

**Figure 4-1.** CLK to ASYNCRST Timing with V(CLKDACTRL) = 1.1V

It is highly recommended to stop the clock at the Low level when ASYNCRST is active (high level). Note that when e2v's ADCs are in reset, the ADC Data Ready output (input clock of the DMUX) is stopped at the low level. In the case where the clock can not be stopped during the reset (note recommended), it is not allowed to have an active edge (rising and falling edge) of the CLK clock within a  $\pm 125$  ps area around the falling edge of ASYNCRST.

The end of the reset occurs at the falling edge of ASYNCRST, and the edge of the Clock has to occur at the minimum 125 ps after the falling edge of ASYNCRST to ensure a proper timing.

The figure presented above is given for V(CLKDACTRL) =  $1/3^*V_{CCD} = 1.1V$ . If V(CLKDACTRL) has a different value, the forbidden area has to be shifted accordingly to V(CLKDACTRL) value. Please refer to Figure 5-9 on page 18 for delay calculation.

For example, assuming ambient temperature and typical supplies, if V(CLKDACTRL) is set to 1.65V, the delay compared to 1.1V is 95 ps - 0 ps = 95 ps. This means that it is forbidden to have an active edge of the clock within -220 ps / 30 ps (the forbidden area is shifted on the left of the above figure).

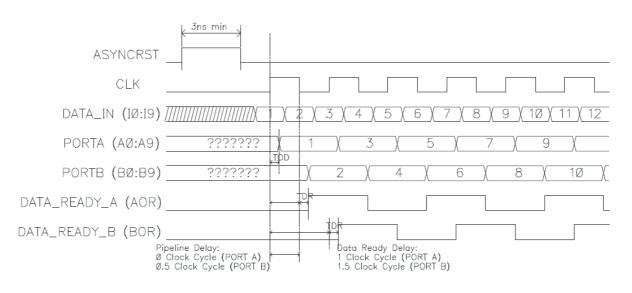

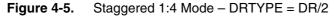

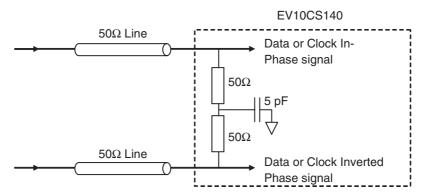

Note: DATA\_READY A = DRA (pin A6) DATA\_READY B = DRB (pin H1)

Note: DATA\_READY A = DRA (pin A6) DATA\_READY B = DRB (pin H1) DATA\_READY C = DRC (pin W5) DATA\_READY D = DRD (pin W16)

### 5. Description of Main Functions

### 5.1 LVDS Input Data and Clock

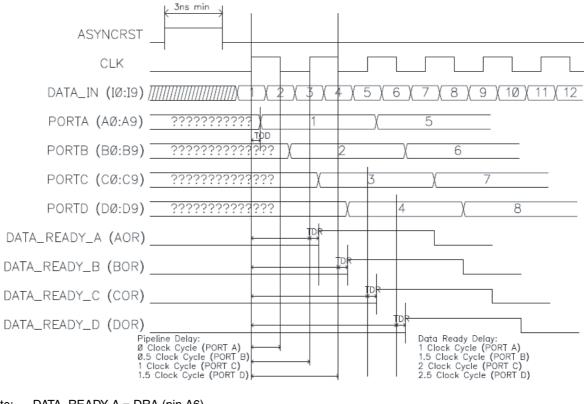

Input data (I0, I0N...19, I9N and IOR, IORN) and clock (CLK, CLKN) are LVDS compatible. They are  $2 \times 50\Omega$  differentially terminated inside the chip as described in Figure 5-1 on page 12. (No need to add external terminated resistors).

Figure 5-1. EV10CS140 LVDS Input Data and Clock Termination Scheme

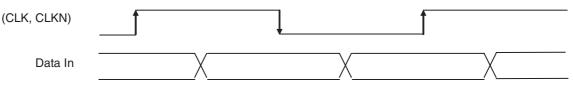

The input clock has to be used in CLK/2 mode (active on rising and falling edge).

#### Figure 5-2. Clock Active on Falling and Rising Edge

### 5.2 Additional Bit (IOR,IORN)

Differential inputs IOR, IORN can be used in simultaneous mode only (not in staggered mode).

When a signal is applied on IOR and IORN, the "additional bit" is activated. It can be used to process the Out of Range bit from the ADC, in which case, the DMUX features an 11-bit input/output data stream.

IOR, IORN is demultiplexed by the selected DMUX ratio:

- In 1:4 ratio, the 11<sup>th</sup> bit is outputted on AOR/DRAN, AORN/DRA, BOR/DRBN, BORN/DRB, COR/DRCN, CORN/DRC and DOR/DRDN, DORN/DRD at a quarter of its initial speed.

- In 1:2 ratio, the 11<sup>th</sup> bit is outputted on AOR/DRAN, AORN/DRA and BOR/DRBN, BORN/DRB at half its initial speed.

- Note: In Staggered output mode: (AORN/DRA, AOR/DRAN), (BORN/DRB, BOR/DRBN), (CORN/DRC, COR/DRCN) and (DORN/DRD, DOR/DRDN) are used as the Data Ready signal (output clock) for each port. In this mode the additional bit is disabled.

### 5.3 LVDS Output Data and Clocks

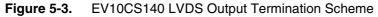

The data (Ax, AxN...Dx, DxN, AOR/DRAN, AORN/DRA...DOR/DRDN and DORN/DRD) and clock outputs (DR, DRN) are LVDS compatible. They must be  $100\Omega$  differentially terminated as close as possible to the differential receiver as described in Figure 5-3.

Note: in 1:2 DMUX Ratio, the unused outputs of Port C and D can be left floating. Refer to Section 5.5 "Programmable DMUX Ratio" on page 14.

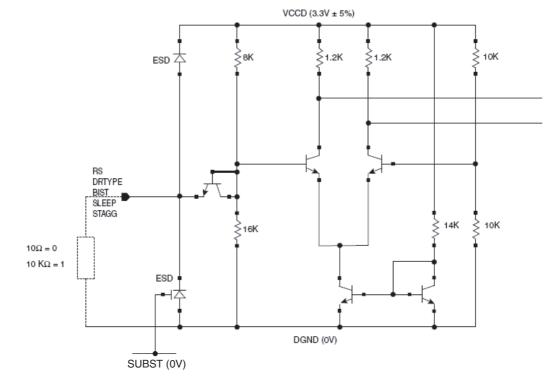

### 5.4 Control Signal Settings

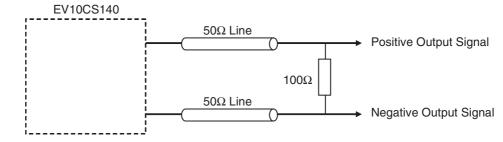

The SLEEP, RS, STAGG, BIST and DRTYPE control signals use the same input buffer.

SLEEP, STAGG, BIST are activated on Logic Low (10 Ohms Grounded or tired to GND), and deactivated on Logic High (10 K $\Omega$  to Ground, or tied to V<sub>CCD</sub> = 3.3V, or left floating).

Figure 5-4. Control Signal Settings (SLEEP, RS, STAGG, BIST and DRTYPE)

| Table 5-1. DMUX Mode Settings – Summa | ry |

|---------------------------------------|----|

|---------------------------------------|----|

|          | Logic | Electric                   | al Level                          |                                                                         |  |  |

|----------|-------|----------------------------|-----------------------------------|-------------------------------------------------------------------------|--|--|

| Function | Level | Static drive Dynamic drive |                                   | Description                                                             |  |  |

|          | 0     | $10\Omega$ to ground       | V(BIST) ≤V <sub>IL</sub>          | BIST (Checker Board generator)                                          |  |  |

| BIST     | 4     | 10 K $\Omega$ to ground    | $\mathcal{M}(PICT) > \mathcal{M}$ | Normal conversion                                                       |  |  |

|          | I     | N/C                        | $V(BIST) \ge V_{IH}$              | Normal conversion                                                       |  |  |

|          | 0     | 10 $\Omega$ to ground      | $V(SLEEP) \leq V_{IL}$            | Power reduction mode (the outputs are fixed at an arbitrary LVDS level) |  |  |

| SLEEP    | 4     | 10 K $\Omega$ to ground    |                                   | Neuroleanuarian                                                         |  |  |

|          | Ι     | N/C                        | $V(SLEEP) \ge V_{IH}$             | Normal conversion                                                       |  |  |

|          | Logic | Electrical Level        |                              |                   |  |

|----------|-------|-------------------------|------------------------------|-------------------|--|

| Function | Level | Static drive            | Dynamic drive <sup>(1)</sup> | Description       |  |

|          | 0     | $10\Omega$ to ground    | $V(STAGG) \le V_{IL}$        | Staggered mode    |  |

| STAGG    | 1     | 10 K $\Omega$ to ground | V(STAGG) ≥ V <sub>IH</sub>   | Simultaneous mode |  |

|          |       | N/C                     |                              |                   |  |

|          | 0     | $10\Omega$ to ground    | $V(RS) \le V_{IL}$           | 1:2 ratio         |  |

| RS       | 1     | 10 K $\Omega$ to ground | V(DC) > V                    | 1:4 ratio         |  |

|          |       | N/C                     | $V(RS) \ge V_{IH}$           |                   |  |

|          | 0     | $10\Omega$ to ground    | V(DRTYPE) ≤ V <sub>IL</sub>  | DR/2 mode         |  |

| DRTYPE   | 1     | 10 K $\Omega$ to ground | $V(DRTYPE) \ge V_{IH}$       | DR mode           |  |

|          |       | N/C                     |                              |                   |  |

Table 5-1.

DMUX Mode Settings – Summary (Continued)

Note: 1. Refer to Table 3-3 on page 6 for logical levels.

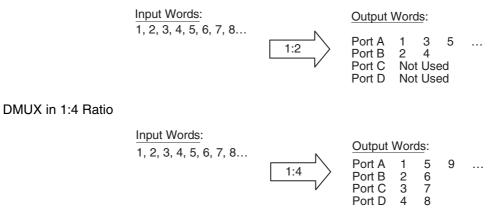

### 5.5 Programmable DMUX Ratio

The demultiplexer ratio is programmable thanks to the RS Ratio selection signal:

| RS | DMUX Ratio |

|----|------------|

| 0  | 1:2        |

| 1  | 1:4        |

DMUX in 1:2 Ratio

Note: in 1:2 mode, unused Port C & D can be left floating.

### 5.6 Data Ready DRTYPE Selection

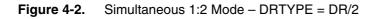

Two modes for the output clock type can be selected by the means of the DRTYPE single-ended digital input.

For proper logic 1 or 0 settings, refer to section Table 3-3 on page 6.

- When DRTYPE is at logic "1", the DMUX is in DR mode for output clocks only the rising edges of the output clocks are active.

- When DRTYPE is at logic "0", the DR/2 mode is activated for output clocks: both the rising and falling edges of the output clocks are active.

Notes: The preferred (and recommended) mode is DR/2.

| Table 5-3. | DMUX Output Clock Type Selection Logical Setting | s |

|------------|--------------------------------------------------|---|

|            |                                                  |   |

| DRTYPE | DMUX Output Clock Type |  |

|--------|------------------------|--|

| 1      | DR                     |  |

| 0      | DR/2                   |  |

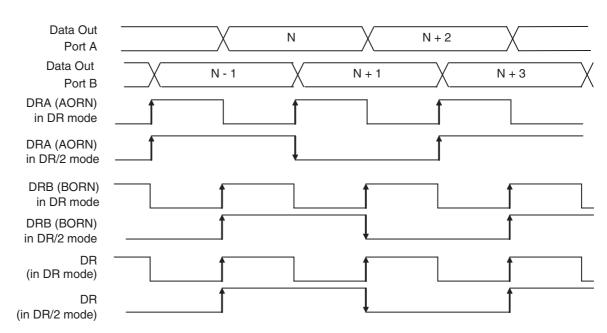

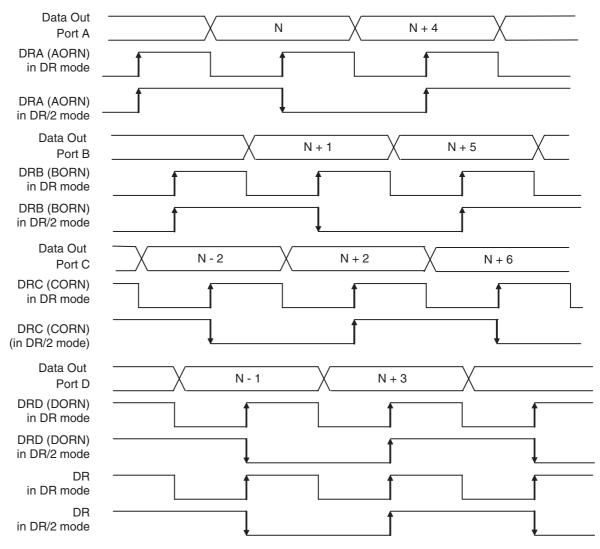

#### 5.7 Output Mode (STAGG)

Two output modes are provided:

- Staggered: the data packets are output one after the other.

- Simultaneous: all the data packets are output at the same time.

In staggered mode, the output clock for each port is provided by the DRA, DRAN, DRB, DRBN, DRC, DRCN and DRD, DRDN signals, which corresponds to AORN, AOR, BRON, BOR, CORN, COR, DORN and DOR respectively.

The Simultaneous mode is the default mode (STAGG left floating or at logic "1"). The Staggered mode is activated by the means of the STAGG input (active low level).

Figure 5-5. Simultaneous Mode in 1:4 ratio (STAGG = 1)

#### Figure 5-6. Staggered Mode in 1:2 ratio (STAGG = 0)

#### **Figure 5-7.** Staggered Mode in 1:4 Ratio (STAGG = 0)

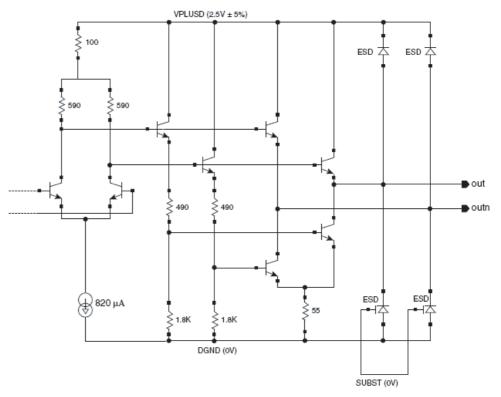

#### 5.8 Asynchronous Reset (ASYNCRST)

The ASYNCRST asynchronous reset input is required to start/initialize the device, and acts as a master reset of the DMUX.

ASYNCRST is activated on Logic HIGH (tied/switched to  $V_{CCD} = 3.3V$ ), and deactivated on Logic LOW (Grounded). Refer to section Table 3-3 on page 6 for logical levels.

During the asynchronous reset, the DMUX' differential clock input (CLK, CLKN) of the DMUX should be stopped at low level (state in which the e2v's single ADC Data Ready signals are when the ADC is in reset).

The ASYNCRST pulse should be last at least 3 ns.

An asynchronous reset is mandatory in order to have a deterministic output data sequence in BIST mode.

### 5.9 Power reduction Mode (SLEEP)

The Power reduction mode saves up to 50% of power consumption. In this mode, the DMUX delivers an arbitrary digital output pattern with LVDS logic states (no toggling).

The Power Reduction mode is enabled by the SLEEP input. SLEEP is activated on logic LOW (grounded), and deactivated on logic HIGH (10 KW to Ground, or tied to  $V_{CCD}$  = 3.3V, or left floating).

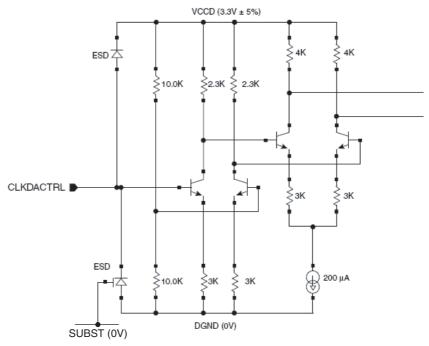

#### 5.10 Clock Input Delay Cell (CLKDACTRL)

A fine tune delay cell is provided to fine-tune the delay between the clock path and the data path at the DMUX input. This adjustment may be necessary depending on the sampling rate and/or if there are misalignments or skews on the different input data. However, data path skews should be maintained below 50 ps.

The delay is controlled by the means of the CLKDACTRL Analog control input. It ranges from -100 ps to 100 ps for CLKDACTRL varying from  $1/3^*V_{CCD}$  to  $2/3^*V_{CCD}$ .

This delay depends on the center position of (CLK, CLKN) Clock path in relation to the digital input data in the DMUX input data paths (I0, I0N) ...(I9, I9N) and (IOR, IORN).

It is recommended to bias CLKDACTRL pin with 1/3\*V<sub>CCD</sub> assuming DEMUX input clock is centered within input data.

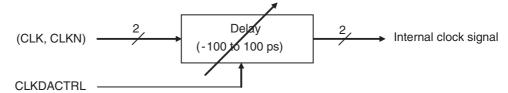

Figure 5-8. Block Diagram of the Clock Input Delay Cell

Figure 5-9. CLKDACTRL Transfer Characteristics of the Delay Cell

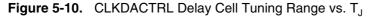

The tuning range is varying linearly over the specified temperature range. The longest tuning range is obtained at hot temperature.

Delay vs Temperature for V(CLKDCATRL) = 1,65V

### 5.11 Built-In Test (BIST)

A Checker Board Pattern might be activated by the means of the BIST input. The BIST is activated on logic LOW (grounded), and deactivated on logic HIGH (10 K $\Omega$  to Ground, or tied to V<sub>CCD</sub> = 3.3V, or left floating).

When activated, the digital outputs correspond to a sequence of "0" and "1". Each bit is toggling at the clock rate. In order to have a deterministic output sequence, it is necessary to perform an asynchronous reset. The output sequence is then:

| BIST sequence | Binary (D9 D0) | Hexa (D9D0) | Binary 11 <sup>th</sup> bit |

|---------------|----------------|-------------|-----------------------------|

| Port A        | 10 1010 1010   | 0x2AA       | 0                           |

| Port B        | 01 0101 0101   | 0x155       | 1                           |

| Port C        | 10 1010 1010   | 0x2AA       | 0                           |

| Port D        | 01 0101 0101   | 0x155       | 1                           |

| Port A        | 01 0101 0101   | 0x155       | 1                           |

| Port B        | 10 1010 1010   | 0x2AA       | 0                           |

| Port C        | 01 0101 0101   | 0x155       | 1                           |

| Port D        |                |             |                             |

Table 5-4.

BIST Output Sequence in 1:4 DMUX Ratio

### 5.12 DMUX Die Junction Temperature Monitoring

If not used the die junction temperature can be left floating or connected to ground.

A die junction temperature measurement setting is available, for maximum junction temperature monitoring (hot point measurement).

The measurement method consists in forcing a 1 mA current into a diode mounted transistor and sensing the voltage across the DIODE pin and the closest available ground pin.

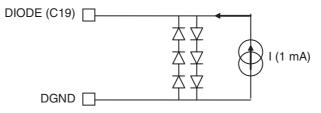

The measurement setup is described in the Figure hereafter:

Figure 5-11. DMUX Diode for Die Junction Temperature Monitoring Setup

CAUTION:

Respect the current source polarity.

In all cases, make sure that the maximum voltage compliance of the current source is limited to a maximum of 1V or use a resistor mounted in series with the current source to avoid damages, which may occur to the transistor device (this may occur for instance if the current source is connected in reverse).

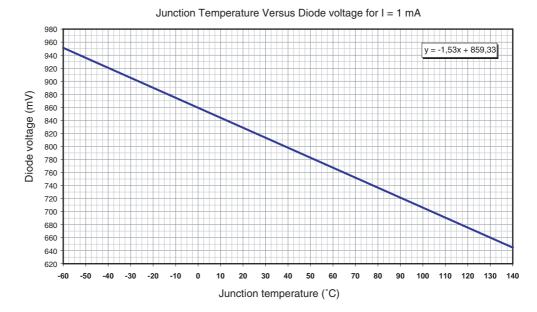

The forward voltage drop ( $V_{DIODE}$ ) across diode component, versus junction temperature, (including chip parasitic resistance), is given below ( $I_{DIODE} = 1mA$ ).

Figure 5-12. Junction Temperature Diode Characteristics

### 6. Applying the EV10CS140

### 6.1 Bypassing, Decoupling and Grounding

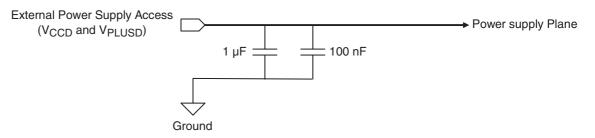

All power supplies have to be decoupled to Ground as close as possible to the signal accesses to the board by 1  $\mu$ F in parallel to 100 nF.

#### Figure 6-1. EV10CS140 Power Supplies Decoupling and Grounding Scheme

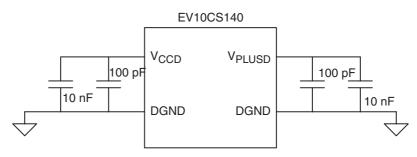

Each group of neighboring power supply pins attributed to the same value should be bypassed with at least one pair of 100 pF in parallel to 10 nF capacitors. These capacitors should be placed as close as possible to the power supply package pins.

The minimum required pairs of capacitors by power supply type is:

- 15 for  $V_{\mbox{\scriptsize CCD}}$

- 14 for  $V_{\text{PLUSD}}$

Figure 6-2. EV10CS140 Power Supplies Bypassing Scheme

### 7. Pin Description

### Table 7-1.Pin Description

| Symbol                                              | Pin Number                                                                                                                                                                                | Function                                                                                                               |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLIES                                      |                                                                                                                                                                                           |                                                                                                                        |

| V <sub>CCD</sub>                                    | C12, C10, C8, C3, D12, D10, D8, D5, D4, D3,<br>E4, E17, E16, G17, G16, G4, G3, J17, J16, K16,<br>K4, K3, L17, L16, N17, N16, R16, T17, T16,<br>T12, T10, T8, T5, T4, T3, U12, U10, U8, U3 | Output 3.3V supply                                                                                                     |

| V <sub>PLUSD</sub>                                  | C15, C14, C13, C11, C9, C7, C6, C5, C4, D13,<br>D11, D9, D7, D6, E3, J4, J3, L4, L3, N4, N3, R4,<br>R3, T14, T13, T11, T9, T7, T6, U15, U14, U13,<br>U11, U9, U7, U6, U5, U4              | Output 2.5V supply                                                                                                     |

| DGND                                                | C18, C17, C16, D17, D14, F17, F16, F4, F3,<br>H17, H16, H4, H3, K17, M17, M16, M4, M3,<br>P17, P16, P4, P3, R17, T15, U19, U18, U17,<br>U16                                               | Ground                                                                                                                 |

| Digital Inputs                                      |                                                                                                                                                                                           |                                                                                                                        |

| 10, 11, 12, 13, 14, 15, 16, 17, 18, 19              | D19, E19, F19, G19, J19, K19, L19, M19, N19,<br>P19                                                                                                                                       | In-phase (+) digital input signal                                                                                      |

| 10n, 11n, 12n, 13n, 14n, 15n, 16n, 17n, 18n,<br>19n | D18, E18, F18, G18, J18, K18, L18, M18, N18,<br>P18                                                                                                                                       | Inverted phase (-) digital input signal                                                                                |

| IORN                                                | B18                                                                                                                                                                                       | In-phase (+) digital input signal additional bit                                                                       |

| IOR                                                 | B19                                                                                                                                                                                       | Inverted phase (–) digital input signal for additional bit                                                             |

| Clock Inputs                                        | ·                                                                                                                                                                                         |                                                                                                                        |

| CLK                                                 | H19                                                                                                                                                                                       | In-phase (+) clock input                                                                                               |

| CLKN                                                | H18                                                                                                                                                                                       | Inverted phase (-) clock input                                                                                         |

| Digital Outputs                                     |                                                                                                                                                                                           |                                                                                                                        |

| A0, A1, A2, A3, A4, A5, A6, A7, A8, A9              | B16, B15, B14, B13, B12, B11, B10, B9, B8, B7                                                                                                                                             | In-phase (+) digital outputs for port A A0 is the LSB, A9 is the MSB                                                   |

| A0N, A1N, A2N, A3N, A4N, A5N, A6N,<br>A7N, A8N, A9N | A16, A15, A14, A13, A12, A11, A10, A9, A8, A7                                                                                                                                             | Inverted phase (-) digital outputs for port A                                                                          |

| AOR/DRAN                                            | В6                                                                                                                                                                                        | In-phase (+) additional bit output for port A<br>or<br>inverted phase (–) output clock in staggered mode<br>for port A |

| AORN/DRA                                            | A6                                                                                                                                                                                        | Inverted phase (–) additional bit output for port A<br>or<br>in-phase (+) output clock in staggered mode for<br>port A |

| B0, B1, B2, B3, B4, B5, B6, B7, B8, B9              | B5, B4, B3, B2, C2, D2, E2, F2, G2, H2                                                                                                                                                    | In-phase (+) digital outputs for port B B0 is the LSB,<br>B9 is the MSB                                                |

| B0N, B1N, B2N, B3N, B4N, B5N, B6N,<br>B7N, B8N, B9N | A5, A4, A3, A2, B1, C1, D1, E1, F1, G1                                                                                                                                                    | Inverted phase (-) digital outputs for port B                                                                          |

| BOR/DRBN                                            | J2                                                                                                                                                                                        | In-phase (+) additional bit output for port B<br>or<br>inverted phase (–) output clock in staggered mode<br>for port B |

#### Table 7-1.Pin Description

| Symbol                                              | Pin Number                                   | Function                                                                                                               |

|-----------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| BORN/DRB                                            | H1                                           | Inverted phase (–) additional bit output for port B<br>or<br>in–phase (+) output clock in staggered mode for<br>port B |

| C0, C1, C2, C3, C4, C5, C6, C7, C8, C9              | M2, N2, P2, R2, T2, U2, V1, V2, V3, V4       | In-phase (+) digital outputs for port C C0 is the LSB, C9 is the MSB                                                   |

| C0N, C1N, C2N, C3N, C4N, C5N, C6N,<br>C7N, C8N, C9N | L1, M1, N1, P1, R1, T1, U1, W2, W3, W4       | Inverted phase (-) digital outputs for port C                                                                          |

| COR/DRCN                                            | V5                                           | In-phase (+) additional bit output for port C<br>or<br>inverted phase (–) output clock in staggered mode<br>for port C |

| CORN/DRC                                            | W5                                           | Inverted phase (–) additional bit output for port C<br>or<br>in-phase (+) output clock in staggered mode for<br>port C |

| D0, D1, D2, D3, D4, D5, D6, D7, D8, D9              | V6, V7, V8, V9, V10, V11, V12, V13, V14, V15 | In-phase (+) digital outputs for port D D0 is the LSB, D9 is the MSB                                                   |

| D0N, D1N, D2N, D3N, D4N, D5N, D6N,<br>D7N, D8N, D9N | W6, W7, W8, W9, W10, W11, W12, W13, W14, W15 | Inverted phase (-) digital outputs for port D                                                                          |

| DOR/DRDN                                            | V16                                          | In-phase (+) additional bit output for port D<br>or<br>inverted phase (–) output clock in staggered mode<br>for port D |

| DORN/DRD                                            | W16                                          | Inverted phase (–) additional bit output for port D<br>or<br>in-phase (+) output clock in staggered mode for<br>port D |

| DR                                                  | J1                                           | In-phase (+) data ready signal output                                                                                  |

| DRN                                                 | К2                                           | Inverted phase (-) data ready signal output                                                                            |

| Additional Functions                                | <u>.</u>                                     | •                                                                                                                      |

| ASYNCRST                                            | B17                                          | Asynchronous reset signal                                                                                              |

| DRTYPE                                              | К1                                           | Output clock type selection signal                                                                                     |

| CLKDACTRL                                           | V19                                          | Clock delay cell control signal                                                                                        |

| RS                                                  | L2                                           | Ratio selection signal                                                                                                 |

| SLEEP                                               | A18                                          | Sleep mode enable                                                                                                      |

| STAGG                                               | A17                                          | Staggered output mode selection signal                                                                                 |

| BIST                                                | V17                                          | Built-in Self Test enable                                                                                              |

| DIODE                                               | C19                                          | Diode for junction temperature monitoring                                                                              |

| NC                                                  | D15, D16, R18, R19, T18, T19, V18, W17, W18  | No connect pins. (Can be connected to any potential for EV10CS140VTPY)                                                 |

### 7.1 EV10CS140 Pinout

Figure 7-1. EBGA 240 (Bottom View)

19 18 17 16 15 14 13 12 8 7 5 3 2 11 10 9 6 4 1 (STAGG) (A7N) (A9N) (a1N) (A3N) (A4N) (A5N) (A6N) (A8N) (BON) (B1N) (b2N) (B3N) (SLEEP) (A0N) (a2N) А AOR (IORIN) A\$YNCR\$T A7 A9 B1 (B4N) IOR ( AO ) A1 ( A2 (A3) A4 ( A5 AG в0 ( в2 ) (вз) A8 В (PLUS) NC (DGND) (DGND) (PLUS) (PLUS) (vccd) (PLUSD) (vccd) V(PLUSD) (vccd) (PLUSD) VPLUSD VPLUSD (PLUSD) (vccd) (в4) B5N С (PLUSD) (vccd) 10 ION (N/C N/C (DGND) (PLUSD) (vccd) (PLUSD) (vccd) (PLUSD) (vccd) (PLUSD) (vccd) (vccd) (вб (B6N) D Е (HN) (VCCD) (PLUS) н (vccd) (vccd) B6 (в7N) F (DGND) (12 12N (DGND) (DGND) (dgnd) B7 B8N 13 ้เร่ง (vccd) (vccd) (VCCD) (vccd) B8 B9N G DRB CLK (clkn) (DGND) (DGND) в9 Н 14 I4N (vccd) (vccd) (PLUSD) (PLUSD) DR J 15 15N (vccd) (VCCD) DRN ORTYPE (vccd) Κ 16 161 (vccd) (vccd) (PLUSD) (PLUSD) RS CON L (DGND) C0 CIN) Μ 17 17N (DGND) (DGND) 18 (PLUSD) 18N (vccd) (vccd) (PLUSD) C1 C2N Ν (DGND) (DGND) Ρ 19 [19N] (DGND) C2 СЗМ (DGND) (PLUSD) NC (PLUSD) 63 C4N NC (vccd) R Т NC NC (vccd) (DGND) (PLUSD) (PLUSD) (vccd) (PLUSD) (vccd) (PLUSD) (vccd) (PLUSD) VPLUSD (vccd) (vccd) (vccd) C4 C5N (vccd) (DGND) (DGND) (DGND) VPLUSD (PLUSD) (vccd) (PLUSD) V(PLUSD) v(PLUSD) VPLUSD v(PLUSD) (PLUS) C5 (PLUSD) (vccd) (vccd) (vccd) C6N U DOR COR DRCN CLKDACTFIL NG віят) D9 C7 D8 D7 D6 D5 D4 D3 D2 D1 DO C9 C8 C6 V NC NC ( D9N DBN D7N DEN (D5N) (D4N D3N (D2N) (D1N DON CON C8N C7N W

### 8. Input/Output Equivalent Schematics

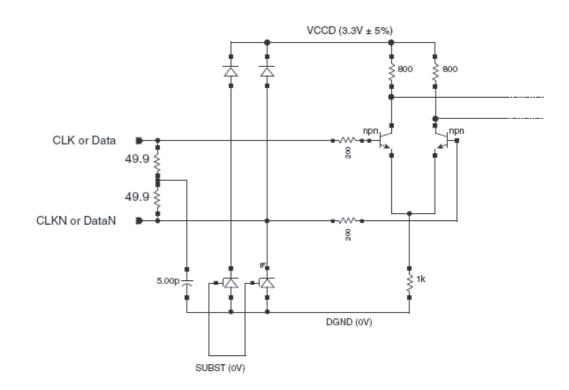

### 8.1 Data and Clock Differential Input Buffer

Figure 8-1. LVDS Data and LVDS Clock Input Buffer

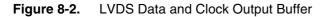

### 8.2 Data and Clock Output Buffer

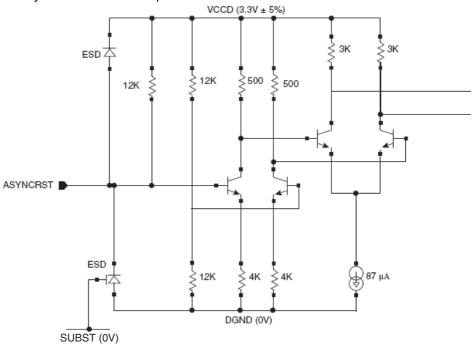

### 8.3 Asynchronous Reset Buffer

### 8.4 Control Signal Input Buffers

Figure 8-4. Control Signals Input Buffers: BIST, STAGG, SLEEP, RS, DRTYPE

### 8.5 CLKDACTRL Delay Cell Control Input Buffer

Figure 8-5. CLKDACTRL Delay Cell Control Input Buffer

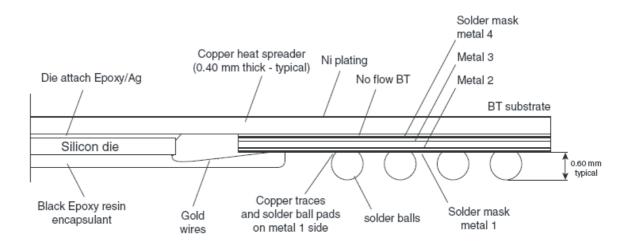

### 9. Package Information

### 9.1 Detailed Cross Section

Note: In the DMUX package (see above), the die's underside is attached to the copper heat spreader so the copper heat spreader is at GND (0V).

It is recommended to electrically isolate the copper heat spreader from the heat sink if a heat sink is used, in which case adequate low Rth electrical isolation should be used.

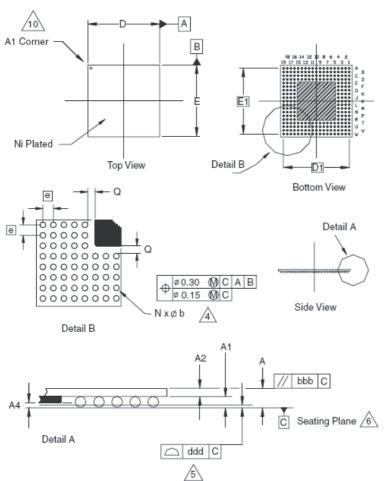

#### 9.2 **Package Outline**

#### Figure 9-2. EBGA 240 Package Outline

| Dimensional References             |             |             |       |  |

|------------------------------------|-------------|-------------|-------|--|

| Ref                                | Min         | Nom         | Max   |  |

| A                                  | 1.25        | 1.45        | 1.60  |  |

| A1                                 | 0.50        | 0.60        | 0.70  |  |

| D                                  | 24.80       | 25.00       | 25.20 |  |

| D1                                 |             | 22.86 (BSC) |       |  |

| E                                  | 24.80       | 25.00       | 25.20 |  |

| E1                                 | 22.86 (BSC) |             |       |  |

| b                                  | 0.70        | 0.80        | 0.90  |  |

| A2                                 | 0.75        | 0.85        | 0.95  |  |

| M                                  |             | 19          |       |  |

| N                                  |             | 240         |       |  |

| bbb                                |             |             | 0.25  |  |

| ddd                                |             |             | 0.20  |  |

| e                                  | 1.27 TYP    |             |       |  |

| A4                                 | 0.15        |             |       |  |

| Q                                  | 0.35        |             |       |  |

| Ref: JEDEC MS-034B Variation BAK-1 |             |             |       |  |

Notes:

- All dimensions are in millimeters

"e" represents the BASIC solder ball grid pitch.

- 3. "M" represents the BASIC solder ball matrix size, and symbol "N" is the maximum allowable number of balls after depolulating.

- A Dimension 'b' is measured at the maximum solder ball

- diameter parallel to primary Datum[C]. Dimension 'ddd" is measured parallel to primary Datum[C]. Primary Datum[C] and seating plane are defined by the spherical crowns of the solder balls.

- Package surface shall be Ni plated. 7

- Encapsulant size may vary with die size. 8. A Black spot for pin 1 identification.

- 10. "A4" is measured at the Edge of encapsulant to the inner Edge of ball pad.

- 11. Dimensioning and tolerancing per ASME Y14.5 1994.

- 12. This drawing is for qualification purpose only.

- Central area on the bottom side of the package (dashed area) corresponds to dam & fill. (Not a solder paste). This area must Note: not to be soldered to PCB.

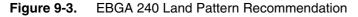

### 9.3 Land Pattern Recommendation

All dimensions are in millimeters

### 9.4 Thermal and Moisture Characteristics

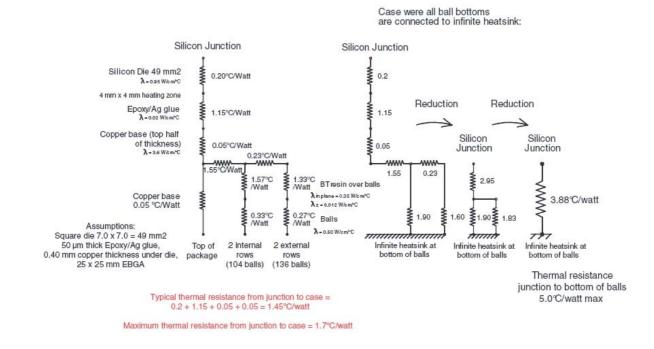

#### Figure 9-4. DMUX Thermal Model for EBGA240 (Typical Values) Derived from ANSYS Thermal Simulation

#### 9.5 Moisture Characteristics

This device is sensitive to the moisture (MSL3 according to JEDEC standard). Its shelf life in sealed bag is 12 months at  $< 40^{\circ}$  C and < 90% relative humidity (RH).

Once the bag is opened, devices that will be subjected to infrared reflow, vapor-phase reflow, or equivalent processing (peak package body temp. 260° C) must be:

- mounted within 168 hours at factory conditions of  $\leq$  30° C/60% RH, or

- stored at ≤20% RH

Before mounting, devices will require baking if the humidity indicator is > 20% when read at  $23^{\circ}$  C ±  $5^{\circ}$  C.

If baking is required, devices may be baked for:

- 192 hours at 40° C + 5° C/-0° C and < 5% RH for low-temperature device containers, or

- 24 hours at 125° C ± 5° C for high-temperature device containers.

| (TOD)   | Digital data Output delay | Delay from the falling edge of the differential clock inputs (CLK, CLKN) (zero crossing point) to the next point of change in the differential output data (zero crossing) with specified load.                                                                                         |

|---------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TDR)   | Data ready output delay   | Delay from the falling edge of the differential clock inputs (CLK, CLKN) (zero crossing point) to the next point of change in the differential output data ready signal (zero crossing) with specified load.                                                                            |

| (PD_D)  | Pipeline Delay on Data    | Number of clock cycles between the data for N being sampled on rising edge of the differential clock inputs (CLK, CLKN) (zero crossing point) and the associated output data for N being made available, (not taking in account the TOD).<br>Total Data propagation delay is PD_D + TOD |

| (PD_DR) | Clock to Data Ready Delay | Number of clock cycles between rising edge of the differential clock inputs (CLK, CLKN) (zero crossing point) and the Data Ready associated to output data for N being made available, (not taking in account the TDR).<br>Total Data Ready propagation delay is PD_DR + TDR            |

| (TR)    | Rise time                 | Time delay for the output DATA signals to rise from 20% to 80% of delta between low level and high level.                                                                                                                                                                               |

| (TF)    | Fall time                 | Time delay for the output DATA signals to fall from 20% to 80% of delta between low level and high level.                                                                                                                                                                               |

### 10. Definition of Terms

### **11. Ordering Information**

#### Table 11-1.Ordering Information

| Part Number   | Package         | Temperature                                         | Screening | Comments |

|---------------|-----------------|-----------------------------------------------------|-----------|----------|

| EV10CS140VTPY | EBGA240<br>RoHS | Industrial grade<br>−40°C < T <sub>amb</sub> < 85°C | Standard  |          |

# e2v

### How to reach us

Home page: www.e2v.com

#### Sales offices:

#### Europe Regional sales office

e2v Itd 106 Waterhouse Lane Chelmsford Essex CM1 2QU England Tel: +44 (0)1245 493493 Fax: +44 (0)1245 492492 mailto: enquiries@e2v.com

#### e2v sas

16 Burospace F-91572 Bièvres Cedex France Tel: +33 (0) 16019 5500 Fax: +33 (0) 16019 5529 mailto: enquiries-fr@e2v.com

#### e2v gmbh

Industriestraße 29 82194 Gröbenzell Germany Tel: +49 (0) 8142 41057-0 Fax: +49 (0) 8142 284547 mailto: enquiries-de@e2v.com

#### Americas

e2v inc 520 White Plains Road Suite 450 Tarrytown, NY 10591 USA Tel: +1 (914) 592 6050 or 1-800-342-5338, Fax: +1 (914) 592-5148 mailto: enquiries-na@e2v.com

#### Asia Pacific

e2v Itd 11/F., Onfem Tower, 29 Wyndham Street, Central, Hong Kong Tel: +852 3679 364 8/9 Fax: +852 3583 1084 mailto: enquiries-ap@e2v.com

#### Product Contact:

e2v Avenue de Rochepleine BP 123 - 38521 Saint-Egrève Cedex France Tel: +33 (0)4 76 58 30 00 **Hotline**: mailto: hotline-bdc@e2v.com

Whilst e2v has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. e2v accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.