## EV8DD700 / EV12DD700 Dual channel Ka-band capable 12 GSps DAC Space Grade

# **Preliminary specification**

#### **OVERVIEW**

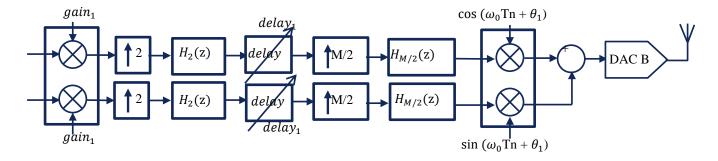

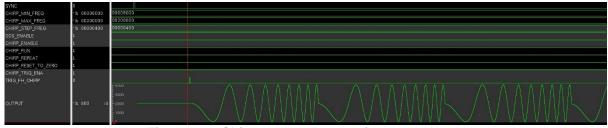

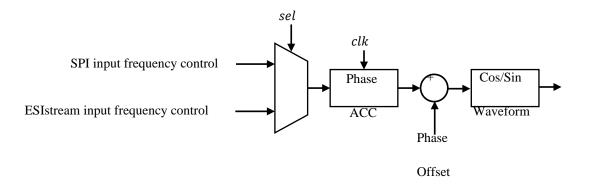

The EV8DD700 / EV12DD700 is a Ka-band capable Rad-tolerant Dual current-steering 8-bit/12-bit Digital-to-Analog converter, with conversion rate up to 12 GSps, synthetizing signals at frequencies over 21GHz without up conversion. This DAC embeds digital features like interpolation, Digital Up Conversion (DUC) and Direct Digital Synthesis (DDS) to reduce input data-rate.

#### FEATURES & MAIN CHARACTERISTICS

- Dual 8-bit/12-bit resolution DAC core

- Conversion rate up to 12 GSps

- -3 dB Analog Bandwidth 25 GHz

- Output signal up to 25 GHz and more

- On chip 100 Ω differential termination

- SPI control

- Programmable Gain

- Selectable output modes:

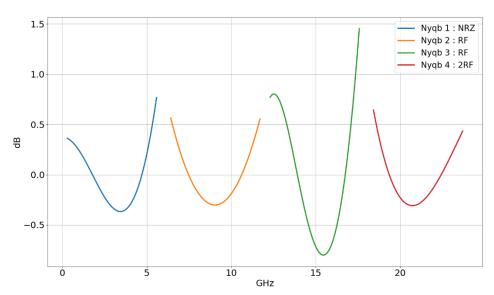

- o Non Return to Zero (NRZ) up to 12 GSps

- o Radio Frequency (RF) up to 12 GSps

- Twice RF (2RF) up to 12 GSps (Fc up to 24 GHz)

- Clock and sync distribution capabilities

- Slow clock for synchronization

- Multi-chip deterministic synchronisation

- Low latency serial link interface with ESIstream protocol, speed up to 12 Gbps

- Bypassable digital interpolation x4, x8 or x16

- Digital Up Conversion (DUC) with 32 bit-NCO

- Frequency hopping

- Digital Direct Synthesis (DDS) with chirp

- Digital Butler Matrix function

- Power consumption 5.8 W to 8.9 W

- 20x20 mm Hi-TCE package

- Temperature range: T<sub>case</sub> = -55 °C to Tj=125 °C

### **APPLICATIONS**

- Radars and jammers

- Instrumentation

- Terrestrial and space telecommunications

- Beamforming

- Software Define Radio

- Direct conversion up to Ka band

#### PERFORMANCE

- Output signal up to 21 GHz

- Fs = 12 GSps Fout up to 3.7 GHz Pout = 0 dBFs NRZ

- o SFDR 70 dBc

- o HD2 or HD3 70 dBc

- o NSD -154.8 dBm/Hz

- Fs = 12 GSps Fout 7.5 GHz Pout = 0 dBFs RF

- o SFDR 60 dBc

- o HD2 or HD3 60 dBc

- NSD -154.8 dBm/Hz

- Fs = 12 GSps Fout 11.5 GHz Pout = 0 dBFs RF

- o SFDR 55 dBc

- o HD2 or HD3 57 dBc

- o NSD -154.8 dBm/Hz

- Fs = 12 GSps (Fc = 24 GHz) Fout 18.5 GHz Pout = 0 dBFs 2RF

- o SFDR 58 dBc

- o HD2 or HD3 58 dBc

- o NSD -154.0 dBm/Hz

- NPR at Fs = 12 GHz over 80% Nyquist zone, at optimum loading factor

- o 1st Nyquist 45 dB (NRZ)

- o 2<sup>nd</sup> Nyquist 40 dB (RF)

- o 3rd Nyquist 37 dB (RF)

- o 4th Nyquist 35 dB (2RF, Fc=24 GHz)

# Table of content

| 1. | REVISION HISTORY                                                           | 3  |

|----|----------------------------------------------------------------------------|----|

| 2. | BLOCK DIAGRAM                                                              | 5  |

| 3. | DESCRIPTION                                                                | 6  |

| 4. | SPECIFICATIONS                                                             | 7  |

|    | 4.1 ABSOLUTE MAXIMUM RATINGS                                               |    |

|    | 4.2 RECOMMENDED CONDITIONS OF USE                                          |    |

|    | 4.3 ELECTRICAL PARAMETERS CHARACTERISTICS FOR SUPPLIES, INPUTS AND OUTPUTS |    |

|    | 4.3.1 EV8DD700 electrical parameters characteristics for supplies          |    |

|    | 4.3.2 EV12DD700 electrical parameters characteristics for supplies         |    |

|    | 4.3.3 Electrical parameters characteristics for Inputs and Ouputs          |    |

|    | 4.4 CONVERTER CHARACTERISTICS                                              |    |

|    | 4.5 TRANSIENT AND SWITCHING CHARACTERISTICS                                |    |

|    | 4.6 DIGITAL OUTPUT CODING                                                  |    |

| 5. | PIN CONFIGURATION AND FUNCTIONS DESCRIPTION                                | 22 |

|    | 5.1 PIN DESCRIPTIONS                                                       |    |

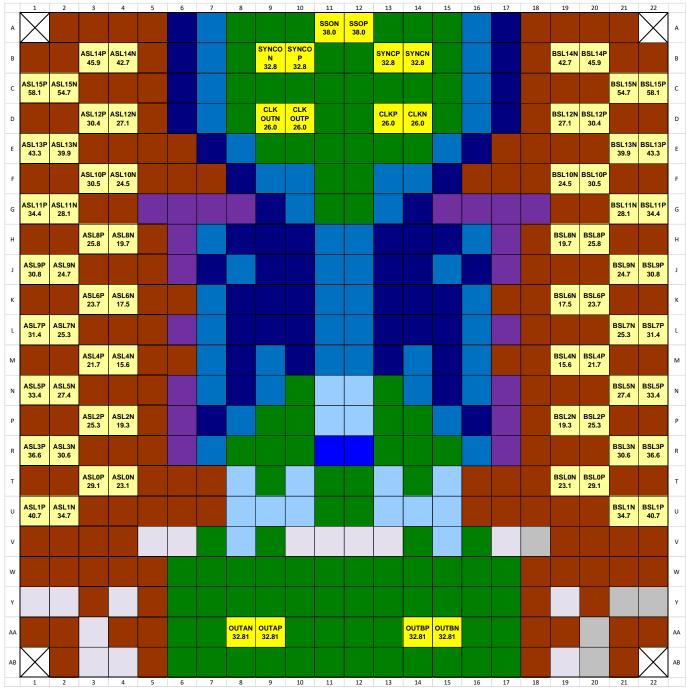

| ;  | 5.2 PINOUT TOP VIEW                                                        |    |

|    | 5.2.1 EV8DD700 pinout top view                                             |    |

|    | 5.2.2 EV12DD700 pinout top view5.3 SKEW ON HSSLS INPUTS                    |    |

| •  | 5.3.1 Introduction                                                         |    |

|    | 5.3.2 EV8DD700 skew on HSSLs inputs                                        |    |

|    | 5.3.3 EV12DD700 skew on HSSLs inputs                                       |    |

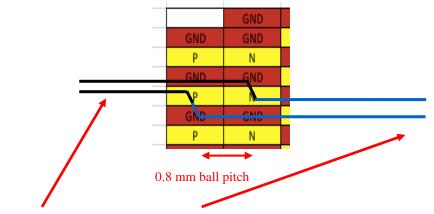

|    | 5.3.4 Routing compensation between N and P                                 |    |

| ;  | 5.4 PINOUT TABLE                                                           | 27 |

| 6. | DEFINITION OF TERMS                                                        | 34 |

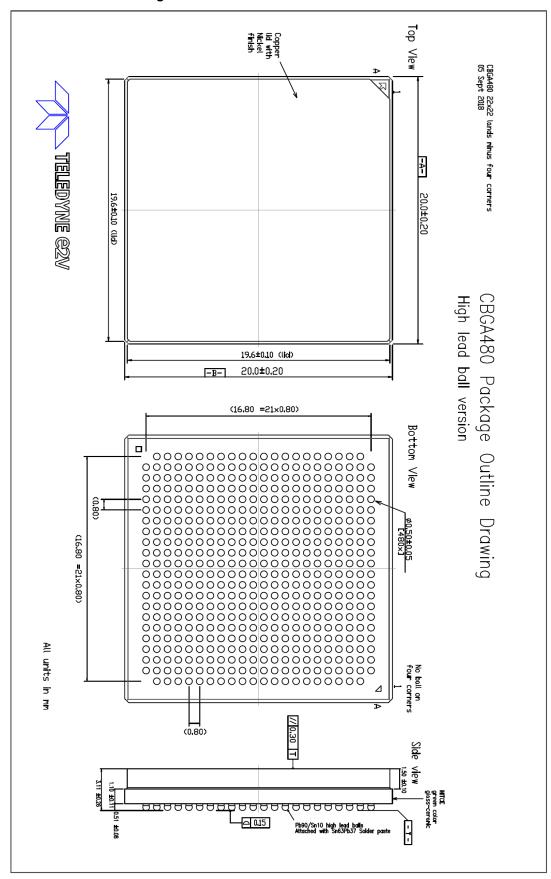

| 7. | PACKAGE DESCRIPTION                                                        | 36 |

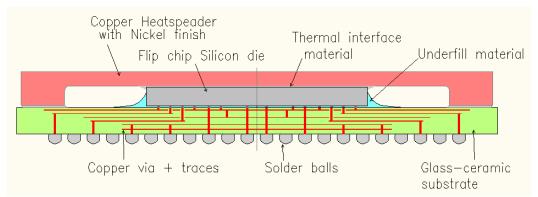

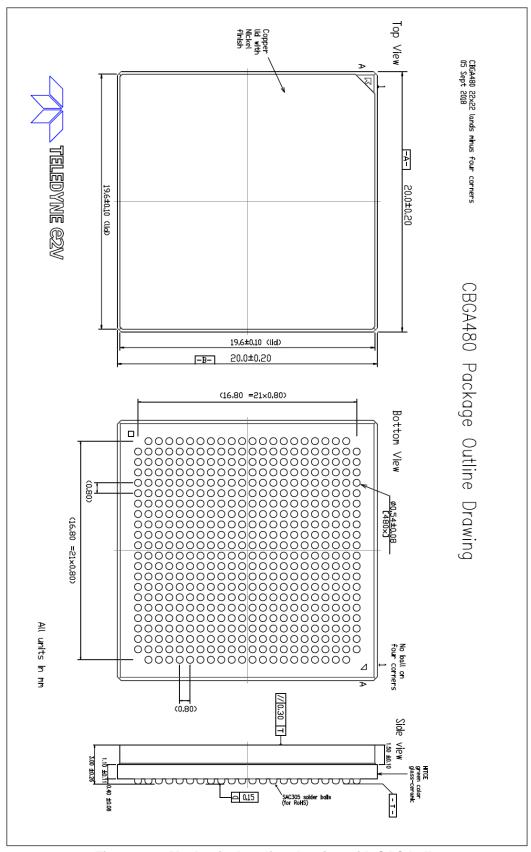

|    | 7.1 Type /Outline                                                          | 36 |

|    | 7.2 MECHANICAL OUTLINE DRAWING                                             | 37 |

|    | 7.2.1 Mechanical outline drawing with SAC balls                            |    |

|    | 7.2.2 Mechanical outline drawing with Pb90Sn10 balls                       |    |

|    | 7.3 THERMAL CHARACTERISTICS                                                | 40 |

| 8. | THEORY OF OPERATION                                                        | 41 |

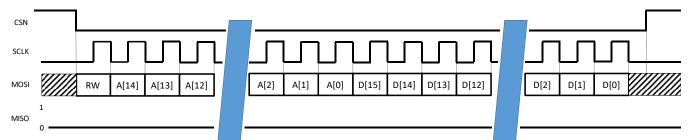

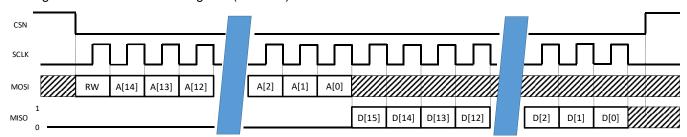

| 9. | SERIAL PERIPHERAL INTERFACE (SPI)                                          | 44 |

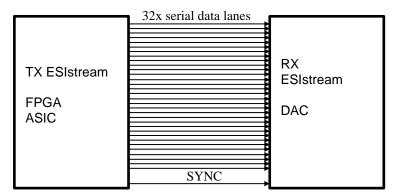

| 10 | . ESISTREAM SERIAL DATA INTERFACE                                          | 45 |

|    | 10.1 SERIAL LINK ANALOG FRONT END                                          | 45 |

|    | 10.2 SERIAL LINK PROTOCOL                                                  | 45 |

|    | 10.2.1 Synchronization                                                     |    |

|    | 10.2.2 Scrambling                                                          |    |

|    | 10.2.3 Encoding                                                            |    |

|    | 10.3 SERIAL LINK IMPLEMENTATION                                            |    |

| 11 | . MAIN FUNCTIONALITIES                                                     | 50 |

|    | 11.1 GAIN ADJUSTMENT                                                       |    |

|    | 11.2 DAC OUTPUT MODES                                                      | 51 |

## EV8DD700 / EV12DD700

| 11.2.1                                                                                                                                          | NRZ output mode                                                                                                                                                                                                                                                                                                                  | 52                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 11.2.2                                                                                                                                          | RF output mode                                                                                                                                                                                                                                                                                                                   |                                      |

| 11.2.3                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                  |                                      |

| 11.3 CL                                                                                                                                         | OCK OUT                                                                                                                                                                                                                                                                                                                          |                                      |

|                                                                                                                                                 | 80                                                                                                                                                                                                                                                                                                                               |                                      |

|                                                                                                                                                 | NC                                                                                                                                                                                                                                                                                                                               |                                      |

|                                                                                                                                                 | /NCO                                                                                                                                                                                                                                                                                                                             |                                      |

|                                                                                                                                                 | E TEMPERATURE MONITORING DIODE                                                                                                                                                                                                                                                                                                   |                                      |

| 11.8 DI                                                                                                                                         | GITAL PROCESSING FUNCTIONS                                                                                                                                                                                                                                                                                                       | 55                                   |

| 11.8.1                                                                                                                                          | Top level description                                                                                                                                                                                                                                                                                                            |                                      |

| 11.8.2                                                                                                                                          | Interpolation                                                                                                                                                                                                                                                                                                                    | 55                                   |

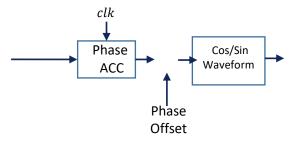

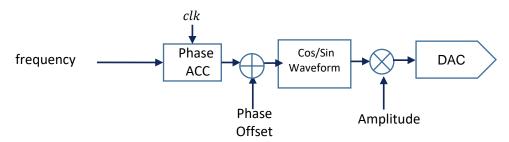

| 11.8.3                                                                                                                                          | NCO                                                                                                                                                                                                                                                                                                                              | 60                                   |

| 11.8.4                                                                                                                                          | Digital Up Conversion (DUC)                                                                                                                                                                                                                                                                                                      | 60                                   |

| 11.8.5                                                                                                                                          | Beamforming and beam-hopping                                                                                                                                                                                                                                                                                                     | 62                                   |

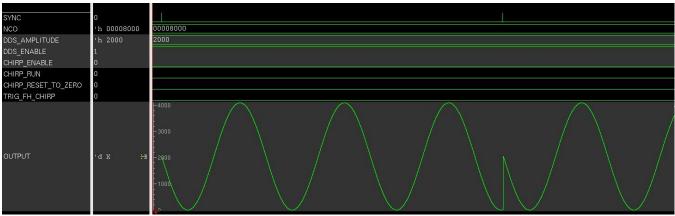

| 11.8.6                                                                                                                                          | Digital Direct Synthesis (DDS) & Chirp mode                                                                                                                                                                                                                                                                                      | 67                                   |

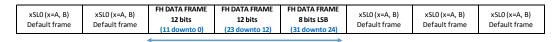

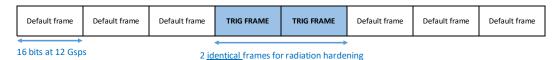

| 11.8.7                                                                                                                                          | Frequency hopping (with DUC)                                                                                                                                                                                                                                                                                                     |                                      |

| 11.8.8                                                                                                                                          | SINC compensation                                                                                                                                                                                                                                                                                                                |                                      |

| 11.8.9                                                                                                                                          | Digital and HSSLs power down                                                                                                                                                                                                                                                                                                     | 81                                   |

| 11.8.10                                                                                                                                         | 7 Test mode                                                                                                                                                                                                                                                                                                                      | 83                                   |

|                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                  |                                      |

| 12. DET                                                                                                                                         | AILED DESCRIPTION OF REGISTERS                                                                                                                                                                                                                                                                                                   | 84                                   |

|                                                                                                                                                 | AILED DESCRIPTION OF REGISTERS                                                                                                                                                                                                                                                                                                   |                                      |

| 12.1 ST                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                  | 84                                   |

| 12.1 ST<br>12.2 RE                                                                                                                              | ART-UP SEQUENCE                                                                                                                                                                                                                                                                                                                  | 84<br>85                             |

| 12.1 ST<br>12.2 RE<br>12.3 RE                                                                                                                   | ART-UP SEQUENCE                                                                                                                                                                                                                                                                                                                  | 84<br>85<br>91                       |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP                                                                                                        | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS LICATION INFORMATION                                                                                                                                                                                                                                                               | 84<br>85<br>91<br><b>121</b>         |

| 12.1 ST<br>12.2 Re<br>12.3 Re<br><b>13. APP</b><br>13.1 PC                                                                                      | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE                                                                                                                                                                                                             | 84<br>91<br><b>121</b>               |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br><b>13. APP</b><br>13.1 PC<br><i>13.1.1</i>                                                                     | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence                                                                                                                                                                                          | 84<br>91<br><b>121</b><br>121        |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br><b>13. APP</b><br>13.1 PC<br>13.1.1<br>13.1.2                                                                  | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  DWER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding                                                                                                                                                   | 84<br>91<br><b>121</b><br>121<br>121 |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3                                                               | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup                                                                                                                                   | 84<br>91<br>121<br>121<br>121        |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br><b>13. APP</b><br>13.1 PC<br>13.1.1<br>13.1.2                                                                  | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode                                                                                                          | 8491121121121123                     |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5                                           | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  DWER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection                                                                                         |                                      |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5                                           | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection                                                                                          |                                      |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5                                           | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection  TERFACES CONFIGURATIONS  DAC analog output                                              |                                      |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.2 INT<br>13.2.1                     | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection  TERFACES CONFIGURATIONS  DAC analog output  DAC clock input                             |                                      |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.2 INT<br>13.2.1<br>13.2.2           | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection  TERFACES CONFIGURATIONS  DAC analog output                                              |                                      |

| 12.1 ST<br>12.2 RE<br>12.3 RE<br>13. APP<br>13.1 PC<br>13.1.1<br>13.1.2<br>13.1.3<br>13.1.4<br>13.1.5<br>13.2 INT<br>13.2.1<br>13.2.2<br>13.2.3 | ART-UP SEQUENCE GISTER SUMMARY GISTER DETAILS  LICATION INFORMATION  WER SUPPLIES RECOMMENDATIONS & POWER-UP SEQUENCE  Power-up sequence  Bypassing, decoupling and grounding  ESD and latchup  Single channel DAC mode  Lid connection  TERFACES CONFIGURATIONS  DAC analog output  DAC clock input.  DAC clock output (CLKout) |                                      |

## 1. REVISION HISTORY

| Issue | Date      | Comments                                  |

|-------|-----------|-------------------------------------------|

| А     | Oct 2019  | Creation from target specification 1188EX |

| A.1   | June 2020 | Removed NDA marking                       |

| A.2   | Sept 2020 | Add EVP12DD700UH P/N                      |

| A.3   | Sept 2020 | P/N modifications                         |

## EV8DD700 / EV12DD700

| Decoupling section modified Power-up sequence updated | B.0 | July 2021 | , , , |

|-------------------------------------------------------|-----|-----------|-------|

|-------------------------------------------------------|-----|-----------|-------|

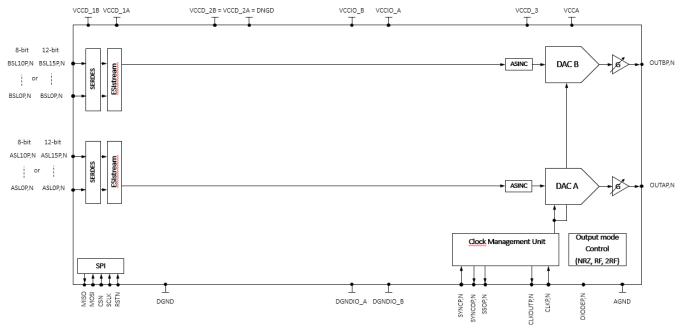

#### 2. **BLOCK DIAGRAM** VCCD\_1B\_VCCD\_1A VCCD\_2B VCCD\_2A VCCIO\_B VCCIO\_A VCCD\_3 VCCA DUC B 8-bit OUTBP.N BSL6P.N BSL8P.N 1 2 Delay ASINC DAC B ESIstream BSL1P,N BSL1P,N NCO B 8-bit 12-bit NCO A ASL6P,N ASL8P,N 2,14,18 OUTAP,N ASINC DAC A ASL1P,N ASL1P,N Delay Int. delay Frac. delay BSLOP,N DUC A Output mode Beam Hopping DDS Beamforming Fast Frequency Clock Management Unit Chirp Control Control Control Control (NRZ, RF, 2RF) Control MISO MOSI CSN SCLK SCLK SYNCOP,N SSOP,N DIODEP,N DGND DGNDIO\_A DGNDIO\_B AGND

Figure 1: Simplified Block Diagram using Digital Up Converters and Digital features

Figure 2: Simplified Block Diagram using Real data

#### 3. DESCRIPTION

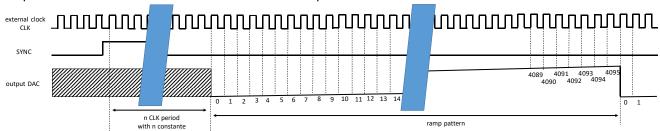

The EV8DD700/EV12DD700 has DUAL 8-bit/12-bit DAC cores, converting at 12 GSps (NRZ and RF modes). Conversion rate is still 12 GSps in 2RF mode using an input clock at 24 GHz. Digital data interface is done through a serial link up to 12Gbps, powered by the ESIstream low latency protocol. The DAC embeds digital features like Digital Up Conversion (DUC) with 3 interpolation ratios, Direct Digital Synthesis (DDS), chirp, Beam-Forming, Beam-Hopping and ultra-fast Frequency Hopping. The sinc(x) = sin(x)/x DAC output response can be compensated through the anti Sinc feature (A-SINC).

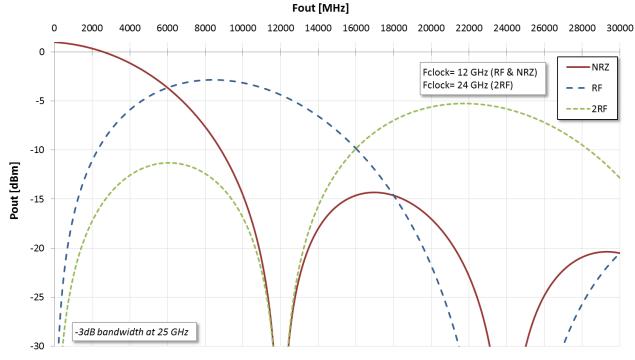

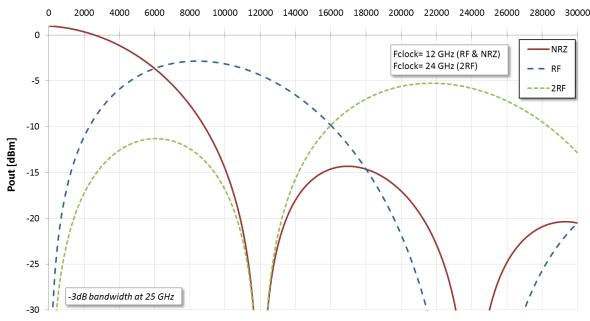

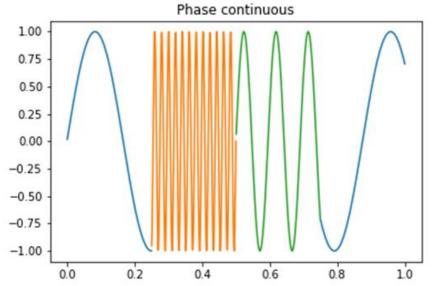

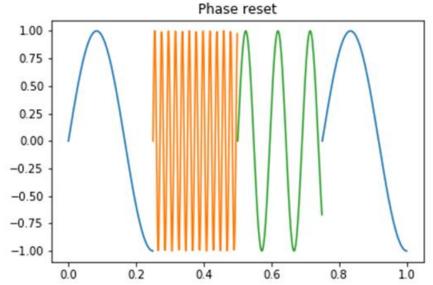

In addition to classical Non Return to Zero output mode (NRZ), the DAC cores have embedded Radio Frequency (RF) mode and 2RF mode requiring a clock at twice the speed of other modes. Thanks to these output modes, the DAC can directly synthetize frequencies up to 21 GHz without the help of any external up converter, enabling very broadband Software Defined Radios with operation from baseband to Ka-band.

Figure 3: Output DAC response at 12GSps in NRZ and RF mode and 2RF mode with 24GHz clock (include the attenuation due to 25GHz output bandwidth, but does not include additional attenuation due to internal parasitics)

The number of serial lanes (11 HSSLs for the EV8DD700 and 16 HSSLs for the EV12DD700 per core) can be adjusted depending on the mode and the instantaneous bandwidth to be transmitted. Using interpolation and digital upconversion (DUC) allows reduction of the required data stream at DAC input. When DUC is used the data type needs to be complex. When no DUC is used, all serial lanes are used and the data type is real. This is described in the table hereafter.

In NRZ and RF modes, the Nyquist Zone NZ = Fc/2 = Fs/2 (with Fs (sampling rate) = Fc (clock rate) = 12GHz, HSSL speed is 12Gbps)

In 2RF mode, the Nyquist Zone NZ = Fc/4 = Fs/2 (with Fs = 12 GHz and Fc = 24GHz, HSSL speed is 12Gbps)

**Table 1.** Impact on serial lanes number depending on interpolation ratio

| Interpolation<br>Ratio | Instantaneous<br>Bandwidth<br>(GHz) | of HSSLs | HSSL<br>speed<br>(Gbps) | Data<br>type |

|------------------------|-------------------------------------|----------|-------------------------|--------------|

|------------------------|-------------------------------------|----------|-------------------------|--------------|

|     |           | (8-bit/12-<br>bit) |    |      |

|-----|-----------|--------------------|----|------|

| x1  | NZ        | 11/16              | Fs | Real |

| x4  | 0.85*NZ/2 | 6/8                | Fs | I+jQ |

| x8  | 0.85*NZ/4 | 3/4                | Fs | I+jQ |

| x16 | 0.85*NZ/8 | 2/2                | Fs | I+jQ |

**Table 2.** Max sampling rate (GSps) per mode (1)

|           | Real mode | Interpolation x4 | Interpolation x8 | Interpolation x16 |

|-----------|-----------|------------------|------------------|-------------------|

| EV8DD700  | 10.8      | 12               | 12               | 12                |

| EV12DD700 | NA        | 12               | 12               | 12                |

<sup>(1)</sup> For NRZ and RF mode, Fc = Fs and for 2RF mode, Fc = 2 Fs

## 4. SPECIFICATIONS

### 4.1 Absolute Maximum Ratings

Absolute maximum ratings are limiting values (referenced to GND = 0 V), to be applied individually, while other parameters are within specified operating conditions.

Exposure above those conditions may cause permanent damage. Long exposure to maximum ratings may affect device reliability

Table 3.

Absolute Maximum ratings

|                                                        |                                      | V          |                                  |         |

|--------------------------------------------------------|--------------------------------------|------------|----------------------------------|---------|

| Parameter                                              | Symbol                               | Min        | Max                              | Unit    |

| Analog supply voltage                                  | Vcca                                 | AGND - 0.3 | 4                                | V       |

| Input/Output supply voltage                            | V <sub>CCIO</sub>                    | GNDO - 0.3 | 2.75                             | V       |

| Digital supply voltage                                 | Vccd                                 | DGND - 0.3 | 1.8TBD                           | V       |

| Serial Link Input peak voltage (with x=0 up to 15)     | Vaslxp - Vaslxn <br> Vbslxp - Vbslxn |            | 2.48V (TBC)                      | Vppdiff |

| Serial Link Input peak voltage                         | ASLxP, ASLxN,<br>BSLxP, BSLxN        | GNDO - 0.3 | V <sub>CCIO</sub> + 0.3<br>(TBC) | V       |

|                                                        |                                      |            |                                  |         |

| Clock input swing (mode ON)                            | VCLKP - VCLKN                        |            | 3.2 (TBC)                        | Vppdiff |

| Clock input swing (mode OFF)                           | VCLKP - VCLKN                        |            | See Note 1                       | Vppdiff |

| Clock input voltage                                    | VCLKP Or VCLKN                       | AGND - 0.3 | Vcca+ 0.3                        | V       |

| SYNC input swing (mode ON)                             | VSYNCP - VSYNCN                      |            | 4                                | Vppdiff |

| SYNC input swing (mode OFF)                            | VSYNCP - VSYNCN                      |            | See Note 1                       | Vppdiff |

| SYNC input peak voltage                                | VSYNCP Or VSYNCN                     | AGND - 0.3 | Vcca+ 0.3                        | V       |

| SPI input voltage                                      | CSN, SCLK, RSTN,<br>MOSI             | DGND - 0.3 | V <sub>CCD</sub> + 0.3<br>(TBC)  | V       |

| Max Junction Temperature                               | T <sub>JMAX</sub>                    |            | 150                              | °C      |

| Storage Temperature                                    | T <sub>stg</sub>                     | -65        | 150                              | °C      |

| VDIODEA input voltage to prevent leakage (VDIODEC=GND) | VDIODEA                              | -0.3       | 0.30                             | V       |

| Maximum input current on DIODE                         | IDIODEA                              |            | 1                                | mA      |

#### Note:

1. For cold sparing application, see Application Note (TBD)

All integrated circuits have to be handled with appropriate care to avoid damages due to ESD. Damage

caused by inappropriate handling or storage could range from performance degradation to complete failure.

Input buffers and associated ESD protection have been designed to allow "cold sparing".

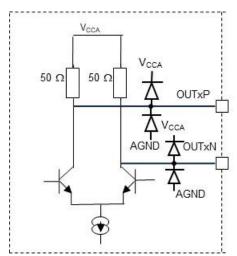

Figure 4: Analog output scheme regarding max ratings

## 4.2 Recommended conditions of use

Table 4. Recommended conditions of use

| Parameter                   | Symbol     | Comments                           | Recommended Value                                  | Unit |

|-----------------------------|------------|------------------------------------|----------------------------------------------------|------|

| Analog supply voltage       | Vcca       | Analog Part                        | 3.3                                                | V    |

| Input/Output supply voltage | Vccio      | Input/Output buffers               | 1.8                                                | V    |

| Digital supply voltage      | Vccd       | Digital buffers                    | 1.175                                              | V    |

| Clock input power level     | PCLK PCLKN |                                    | 1 (TBC)                                            | dBm  |

| Digital CMOS input          | VD         | V <sub>IL</sub><br>V <sub>IH</sub> | 0.00                                               | V    |

| Operating Temperature Range | Tc; TJ     |                                    | -55 °C <t<sub>C ; T<sub>J</sub>&lt; 125 °C</t<sub> | °C   |

## 4.3 Electrical parameters characteristics for supplies, Inputs and Outputs

Unless otherwise specified:

Typical values are given for typical supplies  $V_{CCA}$ = 3.3 V,  $V_{CCD}$  = 1.175 V,  $V_{CCO}$  = 1.8 V at ambient temperature with Fs=12 GHz in default mode (Dual DAC, no DUC nor interpolation, with A-SINC compensation, no beamforming), SSO, CLKOUT and SYNCO disabled.

Minimum and Maximum values are given over temperature.

### 4.3.1 EV8DD700 electrical parameters characteristics for supplies

**Table 5.** EV8DD700 Electrical characteristics for Supplies

| Parameter                                                 | Test<br>Level | Symbol                    | Min  | Тур        | Max  | Unit   | Note |

|-----------------------------------------------------------|---------------|---------------------------|------|------------|------|--------|------|

| RESOLUTION                                                | LOVOI         |                           |      | 8          |      | bit    |      |

| POWER REQUIREMENTS                                        | •             | •                         |      |            |      |        |      |

| Power Supply voltage                                      |               |                           |      |            |      |        |      |

| - Analog                                                  |               | Vcca                      | 3.20 | 3.30       | 3.40 | V      |      |

| - Input/Output                                            |               | V <sub>CCIO</sub>         | 1.70 | 1.80       | 1.90 | V      | (1)  |

| - Digital                                                 |               | Vccd                      | 1.15 | 1.175      | 1.2  | V      |      |

| Power Supply current in NRZ mode                          |               |                           |      |            |      |        |      |

| No digital preprocessing                                  |               |                           |      |            |      |        |      |

| Dual / Single DAC mode                                    |               |                           |      |            |      |        | (2)  |

| - Analog                                                  |               | CCA_NRZ_int1              |      | 1000 / -   |      | mA     | (-)  |

| - Input/Output                                            |               | ICCO_NRZ_int1             |      | 60 / -     |      | mA     |      |

| - Digital                                                 |               | ICCD_NRZ_int1             |      | 1450 / -   | 1    | mA     |      |

| Power Supply current in RF mode                           |               |                           |      |            |      |        |      |

| No digital preprocessing                                  |               |                           |      |            |      |        |      |

| Dual / Single DAC mode                                    |               |                           |      | 4050 / 000 |      | 4      | (2)  |

| - Analog                                                  |               | ICCA_RF_int1              |      | 1050 / 630 |      | mA     | ,    |

| - Input/Output                                            |               | ICCO_RF_int1              |      | 60 / 35    |      | mA     |      |

| - Digital                                                 |               | ICCD_RF_int1              |      | 1450 / 860 |      | mA     |      |

| Power Supply current in 2RF mode No digital preprocessing |               |                           |      |            |      |        |      |

| Dual / Single DAC mode                                    |               |                           |      |            |      |        |      |

| - Analog                                                  |               | look ope :                |      | TBD / -    |      | mA     | (2)  |

| - Analog<br>- Input/Output                                |               | ICCA_2RF_int1             |      | TBD / -    |      | mA     |      |

| - Digital                                                 |               | ICCO_2RF_int1             |      | TBD / -    |      | mA     |      |

| Power Supply current in NRZ mode                          |               | TCCD_ZIXI _IIIt1          |      | 1887       |      | 1117 ( |      |

| Interpolation by 4                                        |               |                           |      |            |      |        |      |

| Dual / Single DAC mode                                    |               |                           |      |            |      |        |      |

| - Analog                                                  |               | ICCA NRZ int4             |      | TBD / -    |      | mA     |      |

| - Input/Output                                            |               | -55/ <u>-</u> [11(2_11(4  |      | ,          |      | `      | (5)  |

| - no beam forming                                         |               | ICCO NRZ int4             |      | TBD / TBD  |      | mA     | (2)  |

| - beam forming                                            |               | I <sub>CCO_NRZ_BFM4</sub> |      | TBD / TBD  |      | mA     |      |

| - Digital                                                 |               |                           |      |            |      |        |      |

| - no beam forming                                         |               | I <sub>CCD_NRZ_int4</sub> |      | TBD / TBD  |      | mA     |      |

| - beam forming                                            |               | ICCD_NRZ_BFM4             |      | TBD / TBD  |      | mA     |      |

| Power Supply current in RF mode                           |               |                           |      |            |      |        |      |

| Interpolation by 4                                        |               |                           |      |            |      |        |      |

| Dual / Single DAC mode                                    |               |                           |      |            |      |        |      |

| - Analog                                                  |               | I <sub>CCA_RF_int4</sub>  |      | TBD / -    |      | mA     |      |

| - Input/Output                                            |               |                           |      |            |      |        | (2)  |

| <ul> <li>no beam forming</li> </ul>                       |               | ICCO_RF_int4              |      | TBD / TBD  |      | mA     | (2)  |

| - beam forming                                            |               | I <sub>CCO_RF_BFM4</sub>  |      | TBD / TBD  |      | mA     |      |

| - Digital                                                 |               | l.                        |      |            |      |        |      |

| - no beam forming                                         |               | CCD_RF_int4               |      | TBD / TBD  |      | mA     |      |

| <ul> <li>beam forming</li> </ul>                          | 1             | ICCD_RF_BFM4              | 1    | TBD / TBD  |      | mA     |      |

| Parameter                                              | Test<br>Level | Symbol                                            | Min | Тур                    | Max | Unit     | Note |

|--------------------------------------------------------|---------------|---------------------------------------------------|-----|------------------------|-----|----------|------|

| Power Supply current in 2RF mode                       |               |                                                   |     |                        |     |          |      |

| Interpolation by 4                                     |               |                                                   |     |                        |     |          |      |

| Dual / Single DAC mode                                 |               |                                                   |     | TDD / TDD              |     |          |      |

| <ul><li>- Analog</li><li>- Input/Output</li></ul>      |               | ICCA_2RF_int4                                     |     | TBD / TBD              |     | mA       |      |

| - no beam forming                                      |               | ICCO_2RF_int4                                     |     | TBD / TBD              |     | mA       | (2)  |

| - beam forming                                         |               | ICCO_2RF_BFM4                                     |     | TBD / TBD              |     | mA       |      |

| - Digital                                              |               |                                                   |     |                        |     |          |      |

| <ul> <li>no beam forming</li> </ul>                    |               | ICCD_2RF_int4                                     |     | TBD / TBD              |     | mA       |      |

| - beam forming                                         |               | I <sub>CCD_2RF_BFM4</sub>                         |     | TBD / TBD              |     | mA       |      |

| Power Supply current in NRZ mode                       |               |                                                   |     |                        |     |          |      |

| Interpolation by 8 Dual / Single DAC mode              |               |                                                   |     |                        |     |          |      |

| - Analog                                               |               | I <sub>CCA_NRZ_int8</sub>                         |     | TBD / -                |     | mA       |      |

| - Input/Output                                         |               | ICCA_NNZ_IIIIO                                    |     | 1.55 /                 |     |          | (0)  |

| - no beam forming                                      |               | ICCO_NRZ_int8                                     |     | TBD / TBD              |     | mA       | (2)  |

| <ul> <li>beam forming</li> </ul>                       |               | I <sub>CCO_NRZ_BFM8</sub>                         |     | TBD / TBD              |     | mA       |      |

| - Digital                                              |               |                                                   |     | TDD / TDD              |     |          |      |

| - no beam forming                                      |               | CCD_NRZ_int8                                      |     | TBD / TBD              |     | mA<br>mA |      |

| - beam forming Power Supply current in RF mode         |               | I <sub>CCD_NRZ_BFM8</sub>                         |     | TBD / TBD              |     | MA       |      |

| Interpolation by 8                                     |               |                                                   |     |                        |     |          |      |

| Dual / Single DAC mode                                 |               |                                                   |     |                        |     |          |      |

| - Analog                                               |               | I <sub>CCA RF int8</sub>                          |     | TBD / -                |     | mA       |      |

| - Input/Output                                         |               |                                                   |     |                        |     |          | (2)  |

| <ul> <li>no beam forming</li> </ul>                    |               | I <sub>CCO_RF_int8</sub>                          |     | TBD / TBD              |     | mA       | (2)  |

| - beam forming                                         |               | I <sub>CCO_RF_BFM8</sub>                          |     | TBD / TBD              |     | mA       |      |

| - Digital                                              |               |                                                   |     | TBD / TBD              |     | - Λ      |      |

| <ul><li>no beam forming</li><li>beam forming</li></ul> |               | I <sub>CCD_RF_int8</sub> I <sub>CCD_RF_BFM8</sub> |     | TBD / TBD              |     | mA<br>mA |      |

| Power Supply current in 2RF mode                       |               | ICCD_RF_BFW6                                      |     | 1007100                |     | 1117 \   |      |

| Interpolation by 8                                     |               |                                                   |     |                        |     |          |      |

| Dual / Single DAC mode                                 |               |                                                   |     |                        |     |          |      |

| - Analog                                               |               | ICCA_2RF_int8                                     |     | TBD / -                |     | mA       |      |

| - Input/Output                                         |               |                                                   |     |                        |     |          | (2)  |

| - no beam forming                                      |               | I <sub>CCO_2RF_int8</sub>                         |     | TBD / TBD<br>TBD / TBD |     | mA       | (-/  |

| <ul><li>beam forming</li><li>Digital</li></ul>         |               | ICCO_2RF_BFM8                                     |     | ושט / ושט              |     | mA       |      |

| - no beam forming                                      |               | ICCD_2RF_int8                                     |     | TBD / TBD              |     | mA       |      |

| beam forming                                           |               | ICCD_2RF_BFM8                                     |     | TBD / TBD              |     | mA       |      |

| Power Supply current in NRZ mode                       |               |                                                   |     |                        |     |          |      |

| Interpolation by 16                                    |               |                                                   |     |                        |     |          |      |

| Dual / Single DAC mode                                 |               |                                                   |     |                        |     |          |      |

| - Analog                                               |               | ICCA_NRZ_int16                                    |     | TBD / -                |     | mA       |      |

| <ul><li>Input/Output</li><li>no beam forming</li></ul> |               | ICCO_NRZ_int16                                    |     | TBD / TBD              |     | mA       | (2)  |

| - beam forming                                         |               | ICCO_NRZ_INT16                                    |     | TBD / TBD              |     | mA       |      |

| - Digital                                              |               | 1000_NNZ_BI WIO                                   |     | ,                      |     |          |      |

| - no beam forming                                      |               | ICCD_NRZ_int16                                    |     | TBD / TBD              |     | mA       |      |

| - beam forming                                         |               | ICCD_NRZ_BFM16                                    |     | TBD / TBD              |     | mA       |      |

| Power Supply current in RF mode                        |               |                                                   |     |                        |     |          |      |

| Interpolation by 16                                    |               |                                                   |     |                        |     |          |      |

| <b>Dual / Single DAC mode</b> - Analog                 |               | ICCA RF int16                                     |     | TBD / -                |     | mA       |      |

| - Input/Output                                         |               | ICCA_KF_INt16                                     |     | 100/-                  |     | 1111/    | 1    |

| - no beam forming                                      |               | ICCO_RF_int16                                     |     | TBD / TBD              |     | mA       | (2)  |

| - beam forming                                         |               | ICCO_RF_BFM16                                     |     | TBD / TBD              |     | mA       |      |

| - Digital                                              |               |                                                   |     |                        |     |          |      |

| - no beam forming                                      |               | ICCD_RF_int16                                     |     | TBD / TBD              |     | mA       |      |

| <ul> <li>beam forming</li> </ul>                       |               | ICCD_RF_BFM16                                     |     | TBD / TBD              |     | mA       | 1    |

| Parameter                                                     | Test<br>Level | Symbol                | Min       | Тур                    | Max | Unit      | Note |

|---------------------------------------------------------------|---------------|-----------------------|-----------|------------------------|-----|-----------|------|

| Power Supply current in 2RF mode                              |               |                       |           |                        |     |           |      |

| Interpolation by 16                                           |               |                       |           |                        |     |           |      |

| Dual / Single DAC mode                                        |               |                       |           |                        |     |           |      |

| - Analog                                                      |               | ICCA_2RF_int116       |           | TBD / -                |     | mA        |      |

| - Input/Output                                                |               |                       |           |                        |     |           | (2)  |

| - no beam forming                                             |               | CCO_2RF_int16         |           | TBD / TBD              |     | mA        | (-)  |

| - beam forming                                                |               | ICCO_2RF_BFM16        |           | TBD / TBD              |     | mA        |      |

| - Digital                                                     |               |                       |           | TDD / TDD              |     | ^         |      |

| - no beam forming                                             |               | CCD_2RF_int16         |           | TBD / TBD<br>TBD / TBD |     | mA<br>m A |      |

| - beam forming                                                |               | ICCD_2RF_BFM16        |           | IBD/IBD                |     | mA        |      |

| Power Supply current standby mode                             |               |                       |           |                        |     |           |      |

| No digital preprocessing Dual / Single DAC mode               |               |                       |           |                        |     |           |      |

| - Analog (NRZ and RF mode)                                    |               | laa.                  |           | TBD / -                |     | mA        |      |

| - Analog (NRZ and RF mode) - Analog (2RF mode with Fc=24 GHz) |               | ICCA<br>ICCA          |           | TBD / TBD              |     | mA        |      |

| - Analog (2RF mode with FC=24 GH2)                            |               | ICCA<br>ICCIO         |           | TBD / -                |     | mA        |      |

| - Inputouipui<br>- Digital                                    |               | I <sub>CCD</sub>      |           | TBD / TBD              |     | mA        |      |

| Power dissipation in NRZ mode                                 |               | ICCD                  |           | 1007100                |     | ША        |      |

| Dual / Single DAC mode                                        |               |                       |           |                        |     |           |      |

| Full power mode without beam forming                          |               |                       |           |                        |     |           |      |

| - no interpolation                                            |               | PD NRZ                |           | 5.1 / -                |     | W         |      |

| - interpolation x4                                            |               | I DINIZ               |           | TBD / TBD              |     | W         |      |

| - interpolation x8                                            |               |                       |           | TBD / TBD              |     | W         | (2)  |

| - interpolation x16                                           |               |                       |           | TBD / TBD              |     | W         | (2)  |

| Full power mode with beam forming                             |               |                       |           | 1007100                |     | **        |      |

| - interpolation x4                                            |               |                       |           | TBD / TBD              |     | W         |      |

| - interpolation x8                                            |               |                       |           | TBD / TBD              |     | W         |      |

| - interpolation x16                                           |               |                       |           | TBD / TBD              |     | W         |      |

| Power dissipation in RF mode                                  |               |                       |           |                        |     |           |      |

| Dual / Single DAC mode                                        |               |                       |           |                        |     |           |      |

| Full power mode without beam forming                          |               |                       |           |                        |     |           |      |

| - no interpolation                                            |               | PDRF                  |           | 5.3 / 3.3              |     | W         |      |

| - interpolation x4                                            |               | . Ditti               |           | TBD / TBD              |     | W         |      |

| - interpolation x8                                            |               |                       |           | TBD / TBD              |     | W         | (2)  |

| - interpolation x16                                           |               |                       |           | TBD / TBD              |     | W         | (-)  |

| Full power mode with beam forming                             |               |                       |           |                        |     |           |      |

| - interpolation x4                                            |               |                       |           | TBD / TBD              |     | W         |      |

| - interpolation x8                                            |               |                       |           | TBD / TBD              |     | W         |      |

| - interpolation x16                                           |               |                       |           | TBD / TBD              |     | W         | 1    |

| Power dissipation (2RF mode)                                  |               |                       |           |                        |     |           |      |

| Dual / Single DAC mode                                        |               |                       |           |                        |     |           |      |

| Full power mode without beam forming                          |               |                       |           |                        |     |           |      |

| no interpolation                                              |               | P <sub>D 2RF</sub>    |           | TBD / -                |     | W         |      |

| - interpolation x4                                            |               |                       |           | TBD / TBD              |     | W         | (2)  |

| <ul> <li>interpolation x8</li> </ul>                          |               |                       |           | TBD / TBD              |     | W         | (2)  |

| <ul> <li>interpolation x16</li> </ul>                         |               |                       |           | TBD / TBD              |     | W         | (3)  |

| Full power mode with beam forming                             |               |                       |           |                        |     |           |      |

| - interpolation x4                                            |               |                       |           | TBD / TBD              |     | W         |      |

| <ul> <li>interpolation x8</li> </ul>                          |               |                       |           | TBD / TBD              |     | W         |      |

| <ul> <li>interpolation x16</li> </ul>                         |               |                       |           | TBD / TBD              |     | W         |      |

| Power dissipation in stand-by mode                            |               | P <sub>D std-by</sub> |           | TBD / 0.5              |     | W         |      |

| Maximum number of power-ups                                   |               | NbPWRup               | 1 million |                        |     |           | (4)  |

#### Note:

- 1. Different VCCD are used for dedicated blocks (VCCD1, VCCD2 and VCCD3).

- 2. Current and power consumption values make the hypothesis that unused features are completely powered down in grounding some VCC values at board level.

- 3. Power consumption makes the assumptions that unused output HSSLs are powered OFF. Refer to Table 21, Table 56 and Table 57.

- 4. Maximum number of power-ups is limited by the maximum number of OTP reading.

## 4.3.2 EV12DD700 electrical parameters characteristics for supplies

**Table 6.** EV12DD700 Electrical characteristics for Supplies

| Parameter                                              | Test<br>Level | Symbol                   | Min  | Тур                     | Max  | Unit     | Note |

|--------------------------------------------------------|---------------|--------------------------|------|-------------------------|------|----------|------|

| RESOLUTION                                             |               |                          |      | 12                      | I.   | bit      |      |

| POWER REQUIREMENTS                                     |               |                          |      |                         |      | <u>'</u> |      |

| Danier Complements                                     |               |                          |      |                         |      |          |      |

| Power Supply voltage - Analog                          |               | Vcca                     | 3.20 | 3.30                    | 3.40 | V        | (1)  |

| - Input/Output                                         |               | VCCA<br>VCCIO            | 1.70 | 1.80                    | 1.90 | V        | (1)  |

| - Digital                                              |               | VCCIO                    | 1.15 | 1.175                   | 1.2  | V        |      |

| Digital                                                |               | VCCD                     | 1.10 | 1.170                   | 1.2  | ľ        |      |

| Power Supply current in NRZ mode                       |               |                          |      |                         |      |          |      |

| No digital preprocessing                               |               |                          |      |                         |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      |                         |      |          | (2)  |

| - Analog                                               |               | ICCA_NRZ_int1            |      | NA                      |      | mA       | (-/  |

| <ul><li>Input/Output</li><li>Digital</li></ul>         |               | ICCO_NRZ_int1            |      | NA<br>NA                |      | mA<br>mA |      |

| Power Supply current in RF mode                        |               | ICCD_NRZ_int1            |      | INA                     |      | IIIA     |      |

| No digital preprocessing                               |               |                          |      |                         |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      |                         |      |          | (=)  |

| - Analog                                               |               | I <sub>CCA_RF_int1</sub> |      | NA                      |      | mA       | (2)  |

| - Input/Output                                         |               | ICCO_RF_int1             |      | NA                      |      | mA       |      |

| - Digital                                              |               | ICCD_RF_int1             |      | NA                      |      | mA       |      |

| Power Supply current in 2RF mode                       |               |                          |      |                         |      |          |      |

| No digital preprocessing                               |               |                          |      |                         |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      | NIA                     |      | A        | (2)  |

| - Analog                                               |               | ICCA_2RF_int1            |      | NA<br>NA                |      | mA<br>mA |      |

| <ul><li>Input/Output</li><li>Digital</li></ul>         |               | ICCO_2RF_int1            |      | NA<br>NA                |      | mA       |      |

| Power Supply current in NRZ mode                       |               | ICCD_2RF_INTI            |      | INA                     |      | IIIA     |      |

| Interpolation by 4                                     |               |                          |      |                         |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      |                         |      |          |      |

| - Analog                                               |               | ICCA_NRZ_int4            |      |                         |      | mA       |      |

| - Input/Output                                         |               |                          |      | 1000 / 650              |      |          |      |

| <ul> <li>no beam forming</li> </ul>                    |               | ICCO_NRZ_int4            |      |                         |      | mA       | (2)  |

| - beam forming                                         |               | ICCO_NRZ_BFM4            |      | 60 / 30                 |      | mA       |      |

| - Digital                                              |               |                          |      | 35 / -                  |      | _        |      |

| - no beam forming                                      |               | ICCD_NRZ_int4            |      | 2500 / 1200             |      | mA<br>mA |      |

| - beam forming                                         |               | ICCD_NRZ_BFM4            |      | 2500 / 1300<br>2300 / - |      | IIIA     |      |

| Power Supply current in RF mode                        |               |                          |      | 23007 -                 |      |          |      |

| Interpolation by 4                                     |               |                          |      | 1095 / 670              |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      |                         |      |          |      |

| - Analog                                               |               | ICCA_RF_int4             |      | 60 / 30                 |      | mA       |      |

| - Input/Output                                         |               |                          |      | 35 / -                  |      |          | (2)  |

| - no beam forming                                      |               | ICCO_RF_int4             |      | 0.000 / 1.000           |      | mA       | (2)  |

| - beam forming                                         |               | ICCO_RF_BFM4             |      | 2500 / 1300             |      | mA       |      |

| - Digital                                              |               | 1                        |      | 2300 / -                |      | A        |      |

| <ul><li>no beam forming</li><li>beam forming</li></ul> |               | ICCD_RF_int4             |      |                         |      | mA<br>mA |      |

| Power Supply current in 2RF mode                       | +             | 1000_KF_BFIVI4           |      |                         |      | 111/7    |      |

| Interpolation by 4                                     |               |                          |      |                         |      |          |      |

| Dual / Single DAC mode                                 |               |                          |      |                         |      |          |      |

| - Analog                                               |               | ICCA_2RF_int4            |      | 1140 / 690              |      | mA       |      |

| - Input/Output                                         |               |                          |      |                         |      |          | (2)  |

| - no beam forming                                      |               | ICCO_2RF_int4            |      | 60 / 30                 |      | mA       | (2)  |

| - beam forming                                         |               | ICCO_2RF_BFM4            |      | 35 / -                  |      | mA       |      |

| - Digital                                              |               |                          |      |                         |      |          |      |

| - no beam forming                                      |               | CCD_2RF_int4             |      | 2500 / 1300             |      | mA<br>A  |      |

| <ul> <li>beam forming</li> </ul>                       |               | ICCD_2RF_BFM4            |      | 2300 / -                |      | mA       |      |

| Parameter                           | Test<br>Level | Symbol                     | Min | Тур         | Max | Unit | Note |

|-------------------------------------|---------------|----------------------------|-----|-------------|-----|------|------|

| Power Supply current in NRZ mode    |               |                            |     |             |     |      |      |

| Interpolation by 8                  |               |                            |     |             |     |      |      |

| Dual / Single DAC mode              |               |                            |     |             |     |      |      |

| - Analog                            |               | ICCA_NRZ_int8              |     | 1050 / 650  |     | mA   |      |

| - Input/Output                      |               |                            |     |             |     |      | (2)  |

| <ul> <li>no beam forming</li> </ul> |               | ICCO_NRZ_int8              |     | 36 / 20     |     | mA   | (2)  |

| <ul> <li>beam forming</li> </ul>    |               | ICCO_NRZ_BFM8              |     | 25 / -      |     | mA   |      |

| - Digital                           |               |                            |     |             |     |      |      |

| <ul> <li>no beam forming</li> </ul> |               | ICCD_NRZ_int8              |     | 2250 / 1160 |     | mA   |      |

| <ul> <li>beam forming</li> </ul>    |               | I <sub>CCD_NRZ_BFM8</sub>  |     | 2110 / -    |     | mA   |      |

| Power Supply current in RF mode     |               |                            |     |             |     |      |      |

| Interpolation by 8                  |               |                            |     |             |     |      |      |

| Dual / Single DAC mode              |               |                            |     |             |     |      |      |

| - Analog                            |               | I <sub>CCA_RF_int8</sub>   |     | 1095 / 670  |     | mA   |      |

| - Input/Output                      |               |                            |     |             |     |      | (2)  |

| <ul> <li>no beam forming</li> </ul> |               | ICCO_RF_int8               |     | 36 / 20     |     | mA   | (2)  |

| <ul> <li>beam forming</li> </ul>    |               | ICCO_RF_BFM8               |     | 25 / -      |     | mA   |      |

| - Digital                           |               |                            |     |             |     |      |      |

| <ul> <li>no beam forming</li> </ul> |               | I <sub>CCD_RF_int8</sub>   |     | 2250 / 1160 |     | mA   |      |

| <ul> <li>beam forming</li> </ul>    |               | I <sub>CCD_RF_BFM8</sub>   |     | 2110 / -    |     | mA   |      |

| Power Supply current in 2RF mode    |               |                            |     |             |     |      |      |

| Interpolation by 8                  |               |                            |     |             |     |      |      |

| Dual / Single DAC mode              |               |                            |     |             |     |      |      |

| - Analog                            |               | I <sub>CCA_2RF_int8</sub>  |     | 1140 / 690  |     | mA   |      |

| - Input/Output                      |               |                            |     |             |     |      | (2)  |

| <ul> <li>no beam forming</li> </ul> |               | I <sub>CCO_2RF_int8</sub>  |     | 36 / 20     |     | mA   | (2)  |

| <ul> <li>beam forming</li> </ul>    |               | I <sub>CCO_2RF_BFM8</sub>  |     | 25 / -      |     | mA   |      |

| - Digital                           |               |                            |     |             |     |      |      |

| - no beam forming                   |               | I <sub>CCD_2RF_int8</sub>  |     | 2250 / 1160 |     | mA   |      |

| beam forming                        |               | ICCD_2RF_BFM8              |     | 2110 / -    |     | mA   |      |

| Power Supply current in NRZ mode    |               |                            |     |             |     |      |      |

| Interpolation by 16                 |               |                            |     |             |     |      |      |

| Dual / Single DAC mode              |               |                            |     |             |     |      |      |

| - Analog                            |               | ICCA_NRZ_int16             |     | 1050 / 650  |     | mA   |      |

| - Input/Output                      |               |                            |     |             |     |      | (2)  |

| <ul> <li>no beam forming</li> </ul> |               | ICCO_NRZ_int16             |     | 25 / 15     |     | mA   | (2)  |

| <ul> <li>beam forming</li> </ul>    |               | ICCO_NRZ_BFM16             |     | 20 / -      |     | mA   |      |

| - Digital                           |               |                            |     |             |     |      |      |

| - no beam forming                   |               | ICCD_NRZ_int16             |     | 2050 / 1060 |     | mA   |      |

| <ul> <li>beam forming</li> </ul>    |               | I <sub>CCD_NRZ_BFM16</sub> |     | 2000 / -    |     | mA   |      |

| Power Supply current in RF mode     |               |                            |     |             |     |      |      |

| Interpolation by 16                 |               |                            |     |             |     |      |      |

| Dual / Single DAC mode              |               |                            |     |             |     |      |      |

| - Analog                            |               | ICCA_RF_int16              |     | 1095 / 670  |     | mA   |      |

| - Input/Output                      |               |                            |     |             |     |      |      |

| - no beam forming                   |               | ICCO_RF_int16              |     | 25 / 15     |     | mA   | (2)  |

| - beam forming                      |               | I <sub>CCO_RF_BFM16</sub>  |     | 20 / -      |     | mA   | ` ′  |

| - Digital                           |               |                            |     |             |     |      |      |

| - no beam forming                   |               | ICCD_RF_int16              |     | 2050 / 1060 |     | mA   |      |

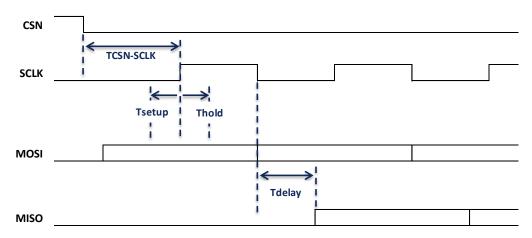

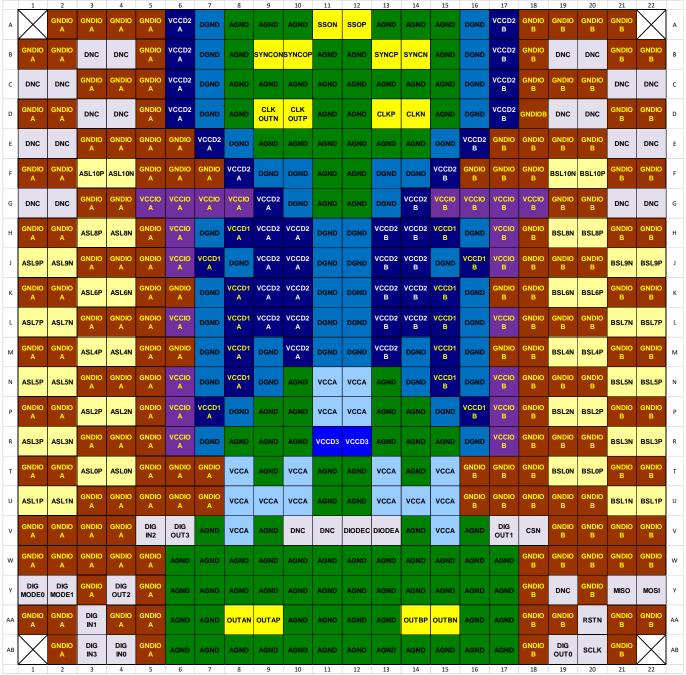

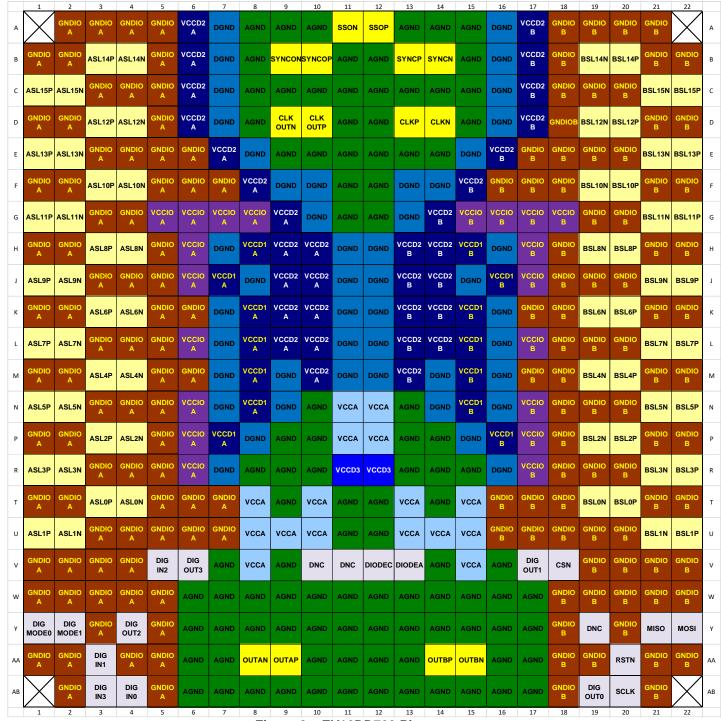

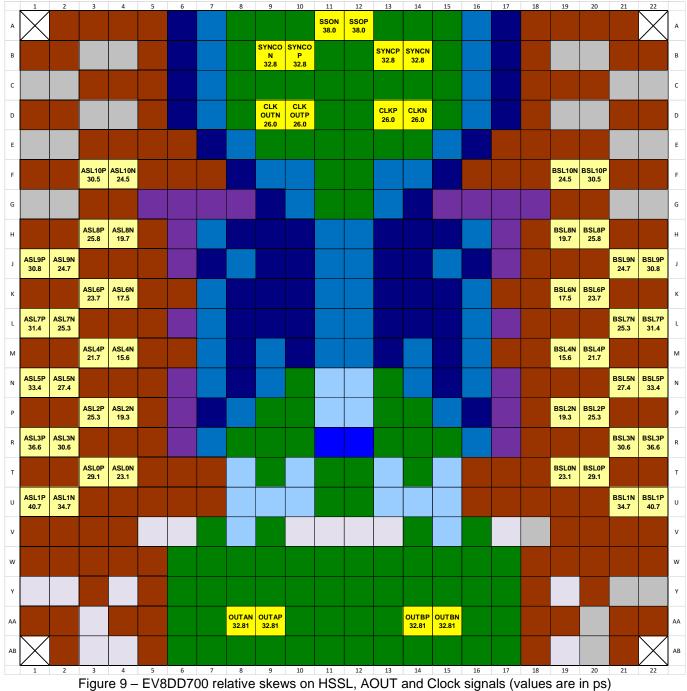

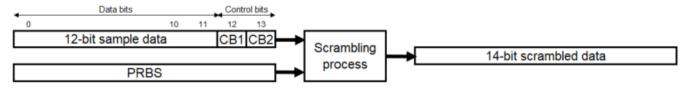

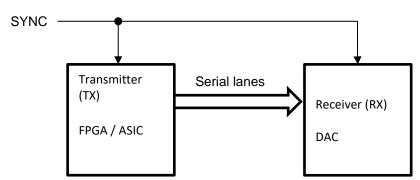

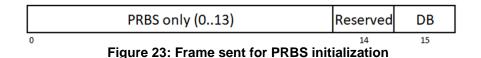

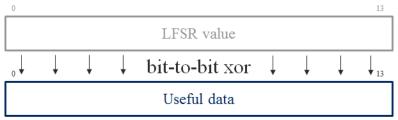

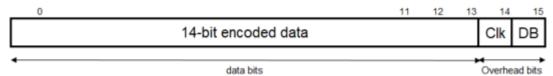

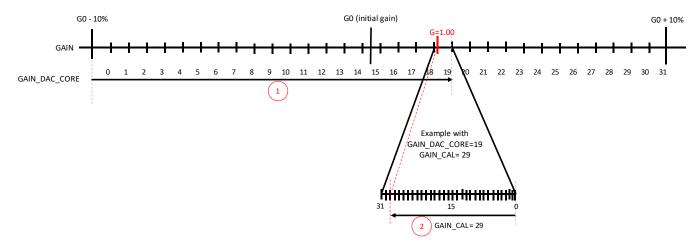

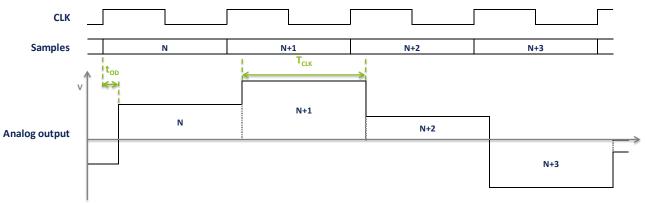

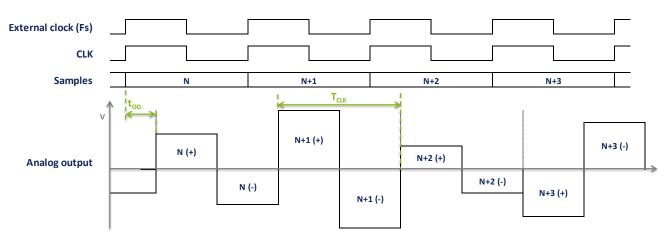

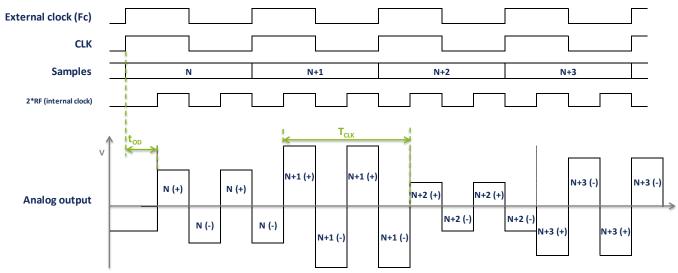

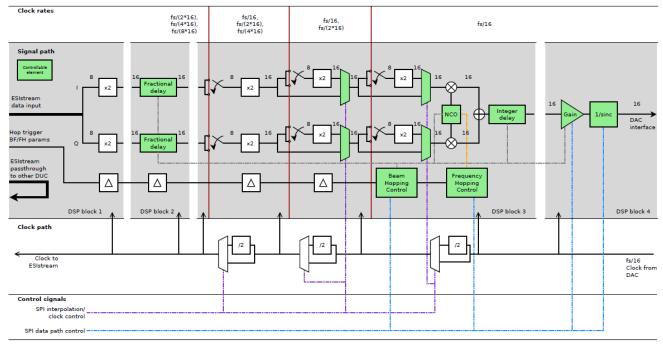

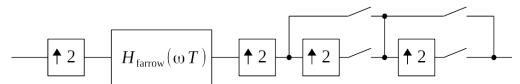

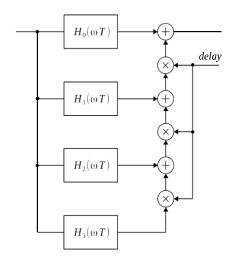

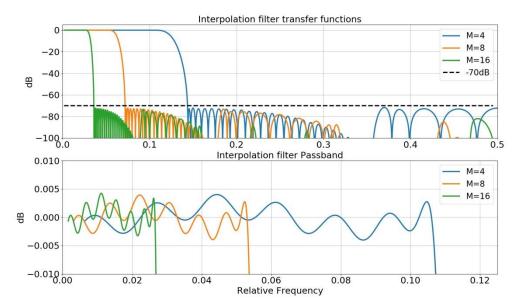

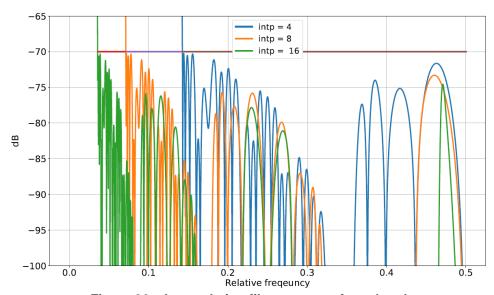

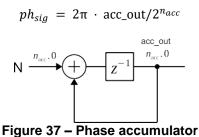

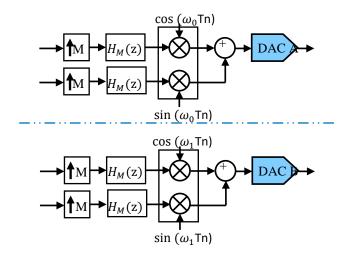

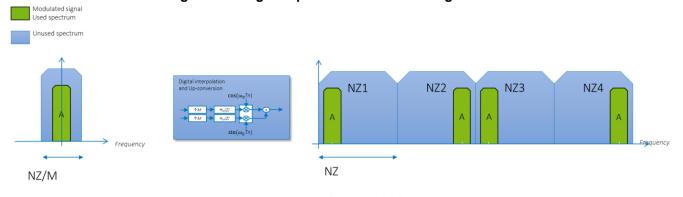

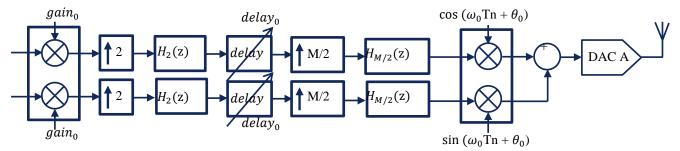

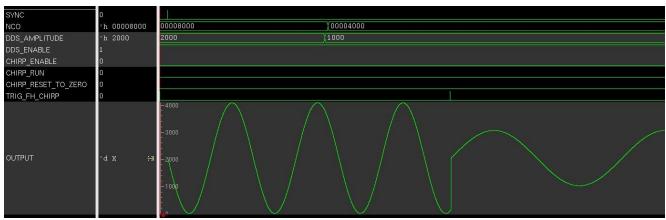

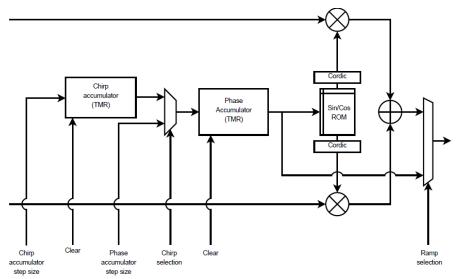

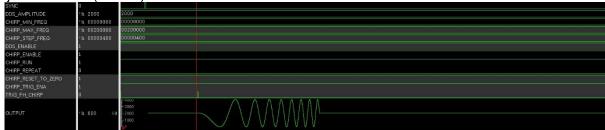

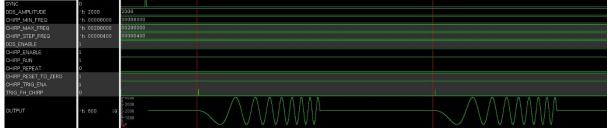

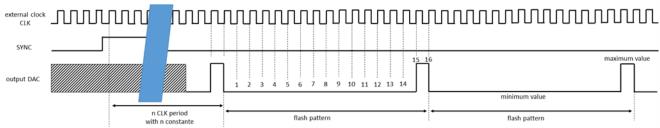

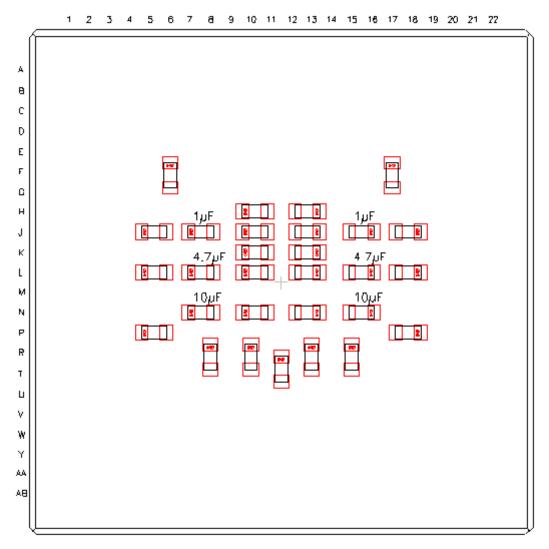

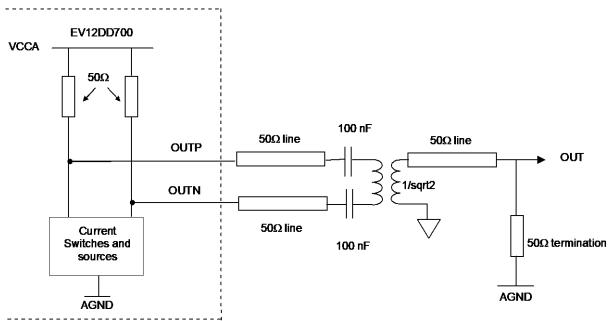

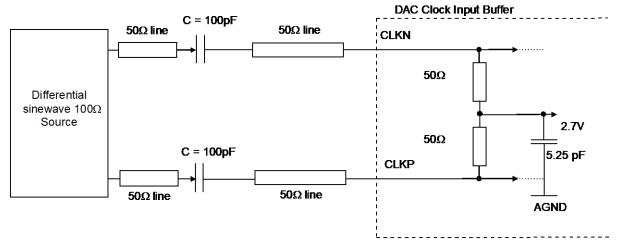

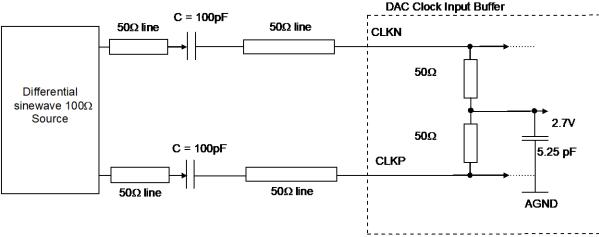

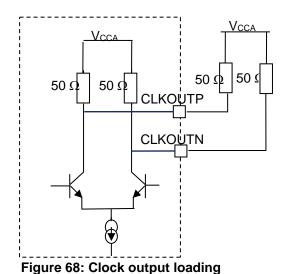

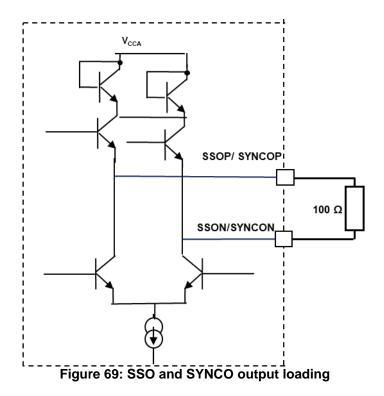

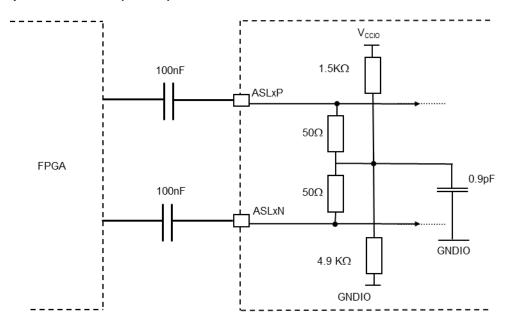

| - beam forming                      |               | ICCD_RF_BFM16              |     | 2000 / -    |     | mA   |      |