# DATASHEET

### **OVERVIEW**

EV12AD550 is a dual S-band capable 12-bit ADC intended for space applications that is built using true single core architecture per channel providing high spectral purity.

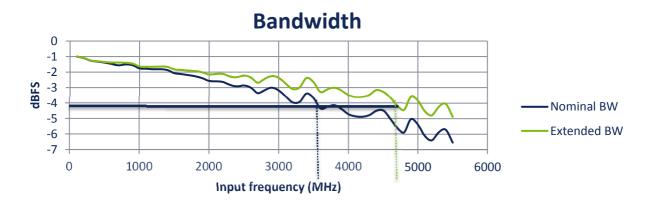

With a 3dB input bandwidth up to 4.3GHz, it allows for direct digitization in S-band without frequency down-conversion. Synthetic Aperture Radar systems will also be able to operate this ADC with reduced dynamic range at frequencies beyond 5GHz (C-band) without frequency downconversion.

This device includes a multiple ADC chained synchronization feature. This would help designing large array of synchronous ADCs to support the development of MIMO systems using digital or hybrid analog/digital beamforming techniques in active antennas.

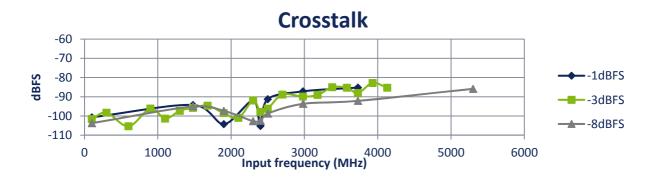

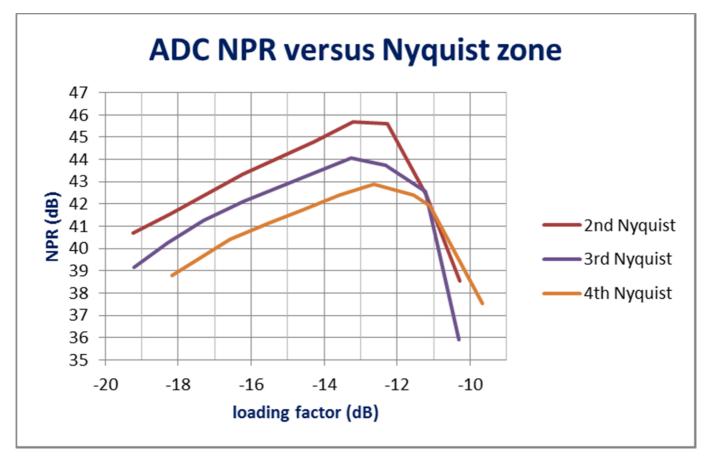

Multichannel applications will benefit from a cross-talk isolation between inputs in excess of 80dB and Noise Power Ratio performance of 50dB in the first Nyquist zone and better than 45dB in the 4<sup>th</sup> Nyquist zone.

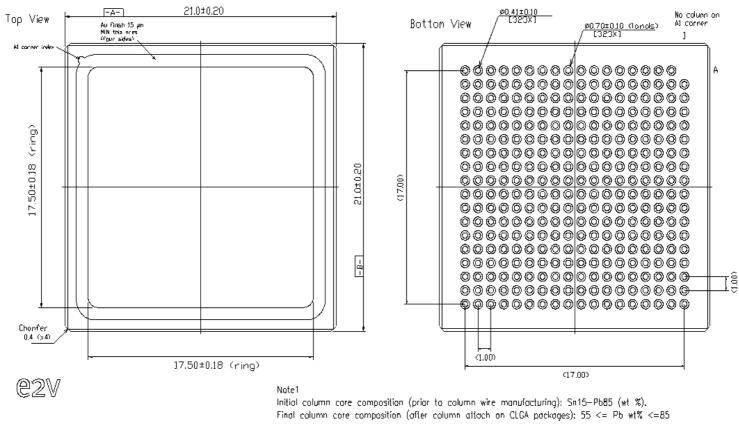

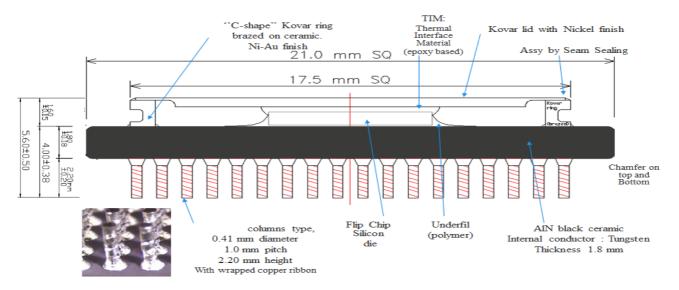

This device comes in a hermetic flip chip CCGA323 package in Aluminum Nitride with improved thermal performance and is planned for QML-V and ESCC certification.

# **APPLICATIONS**

- Earth observation SAR payload

- Telecommunication satellite payload

- Satellite data links

- Satellite altimeter

- Satellite TWTA compensation system

- Satellite to satellite laser data links

## **FEATURES**

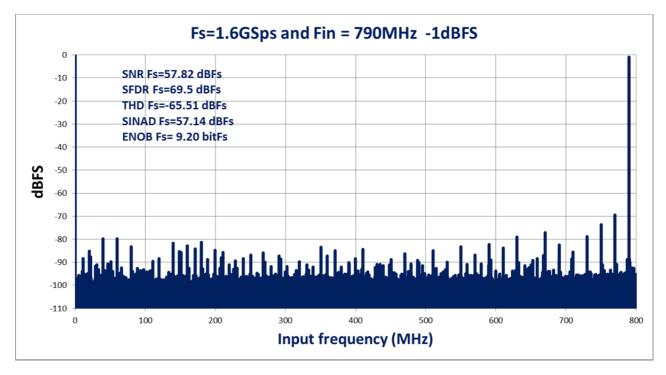

### Dual channel 12-bit 1.6GSps ADC

- Single core architecture ADC per channel

- Differential analog input voltage: 1Vppd

- Full Power Input bandwidth (-3dB): 4.3GHz

- Differential clock input

- Power consumption: 2.3W / channel

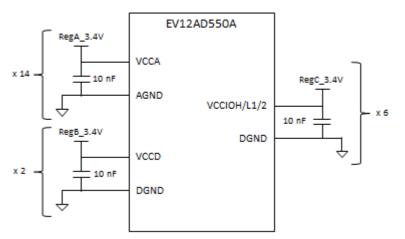

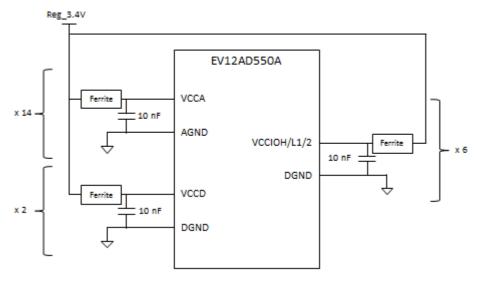

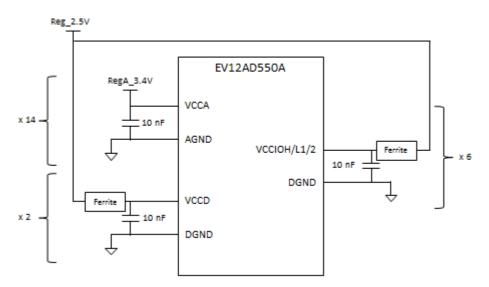

- Power supplies: Single Rail 3.4V or Dual rail 3.4V/2.5V

- Low latency output interface: LVDS DEMUX 1:1 or 1:2

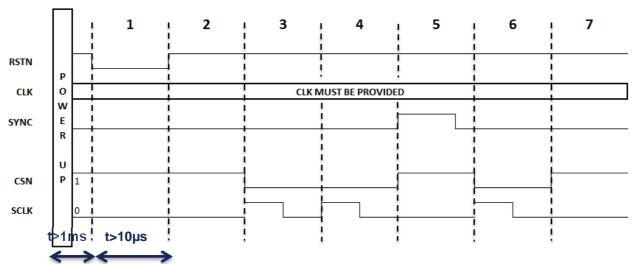

- Package: Hermetic CCGA323 21x21mm / 1mm pitch, Aluminum Nitride material

- SPI configuration with space protection control

- Multiple ADC chained synchronization

- Test mode: ramp, flash, PRBS

- Control bit: parity, in-range, trigger

- Clock input up to 3.2GHz

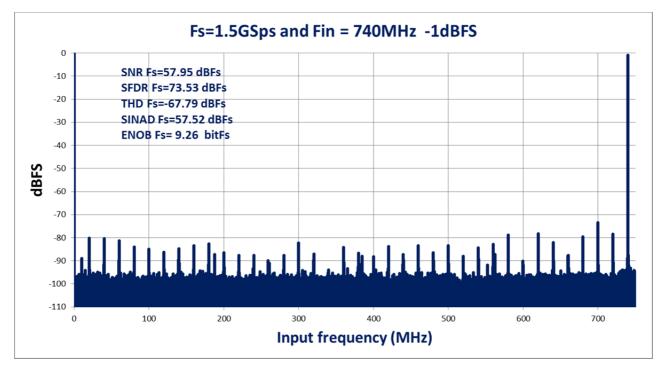

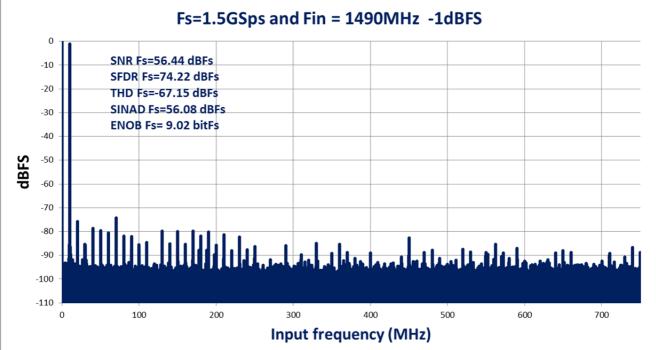

### PERFORMANCE @ 1.5GSps

- 4.3GHz analog input bandwidth (-3dB)

- 50 dB NPR over 1<sup>st</sup> Nyquist

- 47 dB NPR over 2<sup>nd</sup> Nyquist

- 46 dB NPR over 3<sup>rd</sup> Nyquist

- 45 dB NPR over 4<sup>th</sup> Nyquist

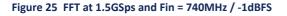

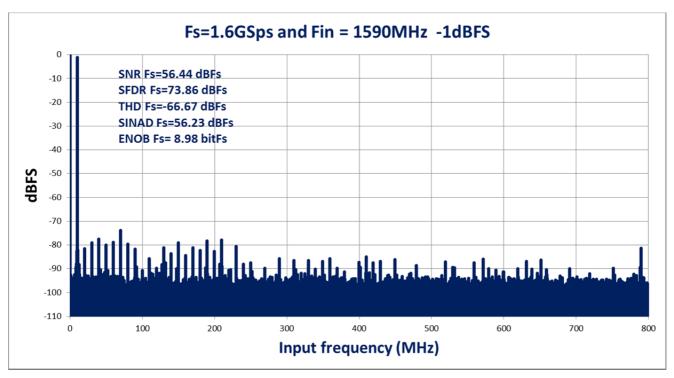

- 76 dBFS SFDR at 100MHz, -1dBFS

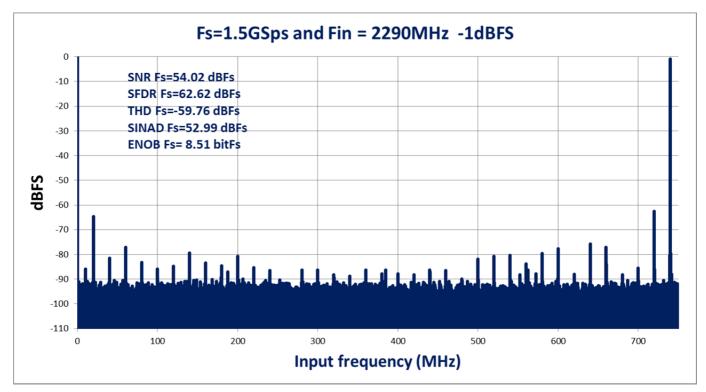

- 70 dBFS SFDR at 1480MHz, -1dBFS

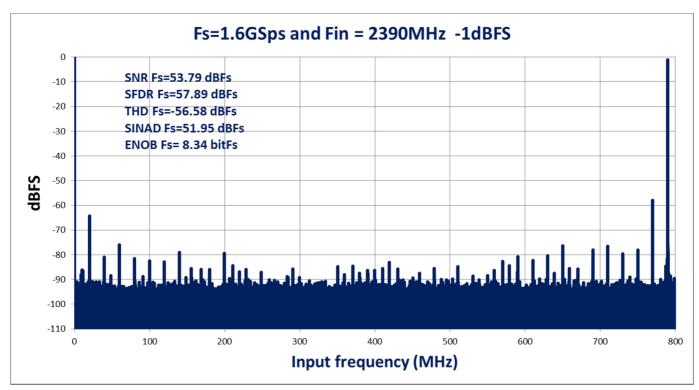

- 75 dBFS SFDR at 1900MHz, -8dBFS

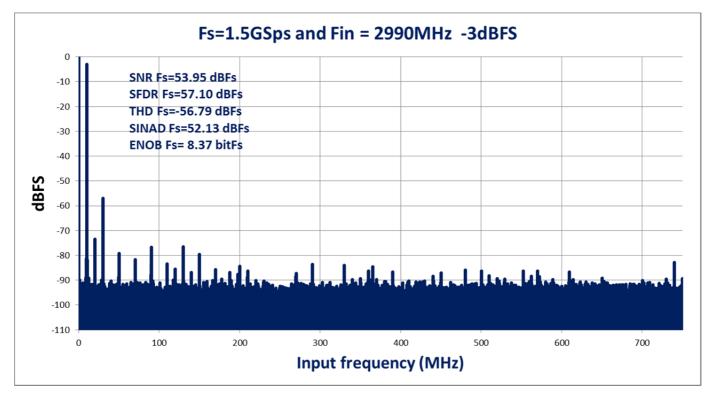

- 68 dBFS SFDR at 3730MHz, -12dBFS

- 59 dBFS SFDR at 5300MHz, -12dBFS

- Latency < 10ns

Whilst Teledyne e2v has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Teledyne e2v accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.

Teledyne e2v Semiconductors SAS, Avenue de Rochepleine, BP 123, 38521 Saint Egrève Cedex France Telephone: +33 (0)476 58 30 00

Facsimile: +33 (0)4

76 58 34 80. Contact Teledyne e2v by e-mail: <a href="mailto:enquiries@teledyne-e2v.com">enquiries@teledyne-e2v.com</a> or visit <a href="mailto:www.teledyne-e2v.com">www.teledyne-e2v.com</a> for global sales and operations centres.

© Teledyne e2v Semiconductors SAS 2018

DS-1198B, February 2019

### 1 Block Diagrams

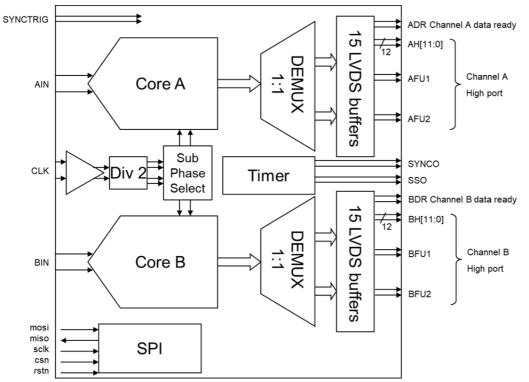

### 1.1 DEMUX 1:1

Figure 1: Block diagram in DEMUX 1:1 output mode

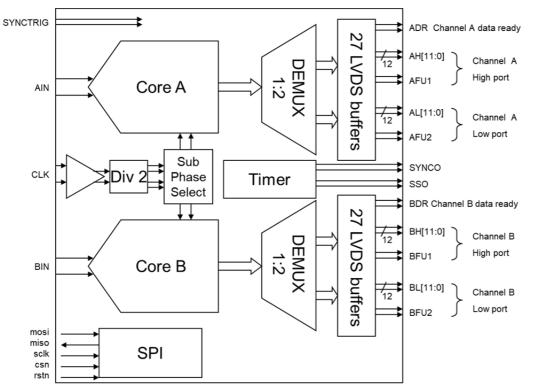

### 1.2 DEMUX 1:2

Figure 2: Block diagram in DEMUX 1:2 output mode

### 2 Description

### 2.1 Description

The EV12AD550 is a dual 12-bit 1.6 GSps ADC featuring low latency LVDS parallel outputs with a built-in selectable 1:2 or 1:1 DEMUX to compromise between power consumption and ease of interfacing.

The two channels can operate in phase or in opposition, thus allowing synchronous or interleaved sampling. Each channel is composed of a true single core ADC sampling at up to 1.6 GSps. Based on an innovative architecture without internal interleaving, it provides high spectral purity. It offers an analog input bandwidth of up to 4.3 GHz with 2 selectable configurations to optimize SNR performance when working in lower Nyquist zones or linearity performance in higher Nyquist zones. It also features a novel synchronization method to ease the synchronization of a large number of ADCs. This device is clocked at twice the sampling rate of each channel. It is controlled through an SPI interface. All sensitive areas of the device have been protected to increase robustness to radiation. This includes, but is not limited to, clock circuitry and SPI registers. A rad hard mode is also provided to increase this robustness of the ADC and prevent potential external influence.

The EV12AD550 is available in a CCGA323 hermetic package using flip-chip assembly and operates over the extended temperature range -55°C top case temperature(Tc); junction temperature (Tj) under +125°C. This package is based on Aluminum Nitride material with enhanced thermal interface to ease power dissipation.

### 2.2 Differences between EV12AD550A & EV12AD550B

EV12AD550A and EV12AD550B are fully pin to pin compatible and digitally compatible. REV B offers new features as described below.

Once fully validated and qualified, the EV12AD550B aims at fully replacing the EV12AD550A. For any question, please contact hotline-bdc@teledyne-e2v.com.

### 1. Sampling Delay Adjust (SDA): increased range

- The revision A offers a SDA range of 10ps. It is improved up to 90ps in the revision B.

### 2. Multi-ADC synchronization: new features

- Revision B embeds a meta-stability detection flag through SPI on the SYNCTRIG input in SYNC mode.

- Revision B includes a new feature to add one clock cycle delay to the timing restart after a SYNC.

Both these features aim at facilitating synchronization of multiple devices or system needing a deterministic sampling.

### 3. Performance: improved H2 & H3 linearity

- The linearity performance on the revision B is slightly improved compared to revision A, especially for high input levels.

### 4. Trigger propagation delay: identical to data path

- The time propagation delay between data path and trigger path is identical in the revision B.

### 5. Sampling Frequency

- The sampling frequency in revision B is extended up to 1.6 GSps (production tests at 1.5 GSps).

### 6. Slight Iccd Current increase

- Compare to revision A, revision B presents a higher Iccd current increase around 50mA-80mA that represents less than 4% of the total power consumption. The thermal model is unchanged.

### **3** Specifications

### 3.1 Absolute maximum ratings

Absolute maximum ratings are limiting and stressing values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Exposure above those conditions may cause permanent damage. Long exposure to maximum ratings may affect device reliability. Functional operation at any other conditions from those indicated in the operational section may affect devices performance and reliability.

**Table 1:** Absolute maximum ratings

| <b>_</b> .                    |                                                                                | Va          | Value      |      |  |

|-------------------------------|--------------------------------------------------------------------------------|-------------|------------|------|--|

| Parameter                     | Symbol                                                                         | Min         | Max        | Unit |  |

| VCCA analog supply voltage    | V <sub>CCA</sub>                                                               | AGND – 0.3  | 3.8        | V    |  |

| VCCIOx output supply voltage  | V <sub>CCIOx</sub>                                                             | GNDIO – 0.3 | 3.8        | V    |  |

| VCCD digital supply voltage   | V <sub>CCD</sub>                                                               | DGND - 0.3  | 3.8        | V    |  |

| Analog input swing (mode ON)  | AIN <sub>P</sub> - AIN <sub>N</sub>  ,<br> BIN <sub>P</sub> - BIN <sub>N</sub> |             | 4.8        | Vppd |  |

| Analog input swing (mode OFF) | AIN <sub>P</sub> - AIN <sub>N</sub>  ,<br> BIN <sub>P</sub> - BIN <sub>N</sub> |             | 1.2        | Vppd |  |

| Analog input voltage          | AIN <sub>P</sub> , AIN <sub>N</sub> , BIN <sub>P</sub> ,<br>BIN <sub>N</sub>   | AGND - 0.3  | 3.6        | v    |  |

| Clock input swing (mode ON)   | [CLK - CLKN                                                                    |             | 4          | Vppd |  |

| Clock input swing (mode OFF)  | [CLK - CLKN                                                                    |             | 1.2        | Vppd |  |

| Clock input voltage           | CLK, CLKN                                                                      | AGND - 0.3  | 3.75       | V    |  |

| SYNC input voltage            | SYNC, SYNCN                                                                    | AGND - 0.3  | VCCA + 0.3 | V    |  |

| SYNC input swing (mode ON)    | SYNC - SYNCN                                                                   |             | 4          | Vppd |  |

| SYNC input swing (mode OFF)   | SYNC - SYNCN                                                                   |             | 1.2        | Vppd |  |

| SPI input voltage             | RSTN, SCLK, CSN,<br>MOSI                                                       | DGND - 0.3  | VCCD + 0.3 | v    |  |

| VDIODEA input voltage         | DIODEA                                                                         | -0.9        | 0.3        | v    |  |

Notes: For cold sparing application, see application note AN1200A.

### Table 2: Absolute maximum ratings (ESD and temperature)

| Parameter                         | Symbol            | Value       | Unit |

|-----------------------------------|-------------------|-------------|------|

| Electrostatic discharge (HBM)     |                   | 750V        | V    |

| ESD classification                | ESD HBM           | CLASS 1B    |      |

| Absolute Max junction temperature | T <sub>JMAX</sub> | 150         | °C   |

| Storage temperature range         | Tstg              | -65 to +150 | °C   |

Notes: All integrated circuits have to be handled with appropriate care to avoid damages due to ESD. Damages caused by inappropriate handling or storage could range from performance degradation to complete failure.

### 3.2 Recommended conditions of use

Table 3: Recommended conditions of use

| Parameter                                  | Symbol                                                                         | Value      | Unit |

|--------------------------------------------|--------------------------------------------------------------------------------|------------|------|

| VCCA analog supply voltage                 | V <sub>CCA</sub>                                                               | 3.4        | V    |

| VCCIOx output supply voltage 1             | V <sub>CCIOx1</sub>                                                            | 3.4 or 2.5 | v    |

| VCCIOx output supply voltage 2             | V <sub>CCIOx2</sub>                                                            | 3.4        | v    |

| VCCD digital supply voltage                | V <sub>CCD</sub>                                                               | 3.4 or 2.5 | V    |

| External clock frequency                   | Fc                                                                             | ≤ 3.2      | GHz  |

| Differential analog input full scale swing | AIN <sub>P</sub> - AIN <sub>N</sub>  ,<br> BIN <sub>P</sub> - BIN <sub>N</sub> | 1.0        | Vppd |

| Differential analog input full scale power | P <sub>A</sub> , P <sub>B</sub>                                                | 1          | dBm  |

| Differential clock input power             | P <sub>CLK</sub>                                                               | 1          | dBm  |

|                                            | V <sub>IL</sub>                                                                | 0          | V    |

| SPI input voltage                          | V <sub>IH</sub>                                                                | VCCD       | v    |

Notes:  $V_{CCIOX1}$  = 2.5V and  $V_{CCD}$  =2.5V can be used to reduce power consumption. Refer to Table 18 in section <u>DEMUX 1:1 or 1:2</u> for more information.

Table 4: Recommended case (Tc) and junction (Tj) temperature conditions of use

| Parameter                                           | Symbol | Value                | Unit |

|-----------------------------------------------------|--------|----------------------|------|

| Operating temperature range (life time < 10 years)  | Tc; Tj | -55 < Tc ; Tj < +125 | °C   |

| Operating temperature range ( life time < 17 years) | Tc; Tj | -55 < Tc ; Tj < +110 | °C   |

Notes: Tj refers to the hot spot junction temperature on the die.

### 3.3 Explanation of test levels

Table 5: Explanation of test levels

| Test<br>level | Comment                                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| 1A            | 100% tested over specified temperature range and specified power supply range                                         |

| 1B            | 100% tested over specified temperature range at typical power supplies                                                |

| 1C            | 100% tested at +25°C over specified supply range                                                                      |

| 1D            | 100% tested at +25°C at typical power supplies                                                                        |

| 2             | 100% production tested at +25°C and samples tested at specified temperatures.                                         |

| 3             | Samples tested only at specified temperatures                                                                         |

| 4             | Parameter value is guaranteed by characterization testing (thermal steady-state conditions at specified temperature). |

| 5             | Parameter value is only guaranteed by design                                                                          |

Only MIN and MAX values are guaranteed

### 3.4 Electrical characteristics for supplies, inputs and outputs

Unless otherwise specified:

- Values are given for typical supplies in single-rail configuration (Refer to Table 18 in section <u>DEMUX 1:1 or 1:2</u> for more information) at Tamb = +25°C; Value between brackets represents value versus temperature.

- Values are given with SDA disabled and reduced swing mode.

- Sampling frequency (Fs) at 1.5 Gsps.

#### Table 6: Electrical characteristics for supplies, inputs and outputs

|                                                                              | Test  |                          |                    | Value     |                       | Unit |      |

|------------------------------------------------------------------------------|-------|--------------------------|--------------------|-----------|-----------------------|------|------|

| Parameter                                                                    | level | Symbol                   | Min                | Тур       | Max                   | Unit | Note |

| Resolution                                                                   |       |                          |                    | 12        |                       | bit  |      |

| POWER REQUIREMENTS                                                           |       |                          |                    |           |                       | •    | •    |

| Power supply voltage                                                         |       |                          |                    |           |                       |      |      |

| Analog                                                                       |       | V <sub>CCA</sub>         | 3.25               | 3.4       | 3.55                  | v    |      |

| • Output                                                                     |       | V <sub>CCIOx1</sub> 3.4V | 3.25               | 3.4       | 3.55                  | v    |      |

|                                                                              | 1A    | V <sub>CCIOx1</sub> 2.5V | 2.35               | 2.5       | 2.65                  | v    | (1)  |

|                                                                              |       | V <sub>CCIOx2</sub>      | 3.25               | 3.4       | 3.55                  | v    |      |

| • Digital                                                                    |       | V <sub>CCD</sub> 3.4V    | 3.25               | 3.4       | 3.55                  | v    |      |

|                                                                              |       | V <sub>CCD</sub> 2.5V    | 2.35               | 2.5       | 2.65                  | v    |      |

| Power supply current in DMUX 1:1                                             |       |                          |                    |           |                       |      |      |

| • Analog, VCCA = 3.4V                                                        |       | I <sub>CCA</sub>         | 950<br>(930)       | 1044      | 1110<br>(1200)        | mA   |      |

| Output 2                                                                     |       |                          |                    |           |                       |      |      |

| Reduced swing, VCCIOH2 = 3.4V                                                |       | I <sub>CCO2</sub>        | 50 (40)            | 63        | 75 (90)               | mA   |      |

| Output 1                                                                     | 1A    |                          |                    |           |                       |      |      |

| Reduced swing, VCCIOH1 = 2.5V                                                | 171   | I <sub>CC01</sub>        | 80 (63)            | 100       | 120 (150)             | mA   | (2)  |

| Reduced swing, VCCIOH1 = 3.4V                                                |       | I <sub>CCO1</sub>        | 80 (60)            | 104       | 120 (153)             | mA   |      |

| • Digital                                                                    |       |                          |                    |           |                       |      |      |

| VCCD = 3.4V                                                                  |       | I <sub>CCD</sub>         | 140 (130)          | 173       | 190 (200)             | mA   |      |

| VCCD = 2.5V                                                                  |       | I <sub>CCD</sub>         | 130 (120)          | 170       | 185 (195)             | mA   |      |

| Power supply current in DMUX 1:2                                             |       |                          |                    |           |                       |      |      |

| • Analog, VCCA = 3.4V                                                        |       | I <sub>CCA</sub>         | 950 (930)          | 1045      | 1110<br>(1200)        | mA   |      |

| • Output 2<br>Reduced swing, VCCIOL2 = 3.4V<br>Reduced swing, VCCIOH2 = 3.4V |       | I <sub>cco2</sub>        | 30 (20)<br>50 (40) | 37<br>64  | 45 (60)<br>75 (90)    | mA   |      |

| Output 1                                                                     |       |                          |                    |           |                       |      |      |

| Reduced swing, VCCIOL1 = 2.5V<br>Reduced swing, VCCIOH1 = 2.5V               | 1A    | I <sub>CC01</sub>        | 50 (40)<br>80 (63) | 74<br>100 | 90 (100)<br>120 (150) | mA   |      |

| Reduced swing, VCCIOL1 = 3.4V<br>Reduced swing, VCCIOH1 = 3.4V               |       | I <sub>CCO1</sub>        | 55 (40)<br>80 (60) | 77<br>104 | 90 (100)<br>120 (153) | mA   |      |

| • Digital                                                                    |       |                          |                    |           |                       |      |      |

| VCCD = 3.4V                                                                  |       | I <sub>CCD</sub>         | 120 (100)          | 155       | 175 (185)             | mA   |      |

| VCCD = 2.5V                                                                  |       | I <sub>CCD</sub>         | 115 (95)           | 148       | 170 (180)             | mA   |      |

|                                                                            | Test Value |                                                                                |           |          |           |                   |      |

|----------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------|-----------|----------|-----------|-------------------|------|

| Parameter                                                                  | level      | Symbol                                                                         | Min       | Тур      | Max       | Unit              | Note |

| Power supply current in full standby mode                                  |            |                                                                                |           |          |           |                   |      |

| Analog                                                                     |            | I <sub>CCA</sub>                                                               | 310 (300) | 334      | 360 (400) | mA                |      |

| • Output (DMUX 1:1)                                                        | 1A         | I <sub>cco</sub>                                                               | 155 (140) | 168      | 190 (235) | mA                | (2)  |

| Output (DMUX 1:2)                                                          |            | I <sub>cco</sub>                                                               | 250 (200) | 278      | 310 (470) | mA                |      |

| <ul> <li>Digital</li> </ul>                                                |            |                                                                                | 45 (40)   | 72       | 85 (94)   | mA                |      |

| • Digital<br>Power dissipation                                             |            | I <sub>CCD</sub>                                                               | 45 (40)   | 72       | 65 (94)   | IIIA              |      |

| (VCCA = VCCD = VCCIOxx = 3.4V)                                             |            |                                                                                |           |          |           |                   |      |

| DEMUX1:1 - Reduced swing                                                   | 1A         | P <sub>D</sub>                                                                 |           | 4.7      | 5.0 (5.3) | w                 | (2)  |

| DEMUX1:2 - Reduced swing                                                   |            |                                                                                |           | 5.0      | 5.3 (5.7) | w                 |      |

| Power dissipation (VCCA = VCCIOx2 = 3.4V, VCCD = VCCIOx1 = 2.5V)           |            |                                                                                |           |          |           |                   |      |

| • DEMUX1:1 - Reduced swing                                                 | 1A         | P <sub>D</sub>                                                                 |           | 4.4      | 4.7 (5.0) | W                 | (2)  |

| DEMUX1:2 - Reduced swing                                                   |            |                                                                                |           | 4.7      | 5 (5.3)   | W                 |      |

| Power dissipation in full standby mode                                     |            |                                                                                |           |          |           |                   |      |

| <ul><li>(VCCA = VCCD = VCCIOxx = 3.4V)</li><li>DEMUX1:1</li></ul>          | 1A         |                                                                                |           | 1.6      | 2.1 (2.2) | w                 | (2)  |

|                                                                            |            | P <sub>D</sub>                                                                 |           |          |           |                   | ( )  |

| DEMUX1:2 -                                                                 |            |                                                                                |           | 1.9      | 2.5 (2.6) | W                 |      |

| ANALOG INPUTS                                                              |            |                                                                                |           | AC DC    |           |                   | (2)  |

| Analog input coupling                                                      |            |                                                                                |           | AC or DC | 1         |                   | (3)  |

| Analog input common mode voltage                                           | 4          |                                                                                |           | 2.4      |           | V                 | (4)  |

| Analog differential input full scale voltage                               | 4          | AIN <sub>P</sub> - AIN <sub>N</sub>  ,<br> BIN <sub>P</sub> - BIN <sub>N</sub> |           |          | 1         | Vppd              |      |

| Analog differential input full scale power (100Ω differential termination) | 4          | P <sub>IN</sub>                                                                |           |          | 1         | dBm               |      |

| Analog input leakage current                                               | 5          | l <sub>iN</sub>                                                                |           | 40       |           | μΑ                |      |

| Analog input resistance                                                    |            |                                                                                |           |          |           |                   |      |

| Without trimming                                                           | 4          | R <sub>IN</sub>                                                                | 80        | 100      | 120       | Ω                 | (5)  |

| With trimming                                                              |            |                                                                                | 95        | 100      | 105       | Ω                 |      |

| Crosstalk between analog inputs                                            | 4          | Xtalk                                                                          |           | 80       |           | dB                | (6)  |

| CLOCK INPUTS                                                               |            |                                                                                |           |          |           |                   |      |

| Clock common mode voltage                                                  | 4          | V <sub>CCM</sub>                                                               | 2.40      | 2.57     | 2.75      | V                 |      |

| Clock differential input power (100 $\Omega$ differential termination)     | 4          | P <sub>CLK</sub>                                                               | -3        | 1        | 7         | dBm               |      |

| Clock input capacitance                                                    | 5          | C <sub>CLK</sub>                                                               |           | 1        |           | pf                |      |

| (including die and package)<br>Clock differential input resistance         | 4          | R <sub>CLK</sub>                                                               | 80        | 100      | 120       | Ω                 |      |

| Clock slew rate                                                            |            | SR <sub>CLK</sub>                                                              | 8         | 12       | 120       | GV/s              |      |

| Clock jitter (3GHz sine wave)                                              |            |                                                                                | 0         | 12       |           |                   |      |

| Integrated from 10MHz to 10GHz                                             |            | Jitter                                                                         |           |          | 100       | fs <sub>rms</sub> |      |

| Intrinsic clock jitter - SDA off                                           | 5          | Intrinsic jitter                                                               |           | 135      |           | fs <sub>rms</sub> |      |

| - SDA on                                                                   | 5          |                                                                                |           | 200      |           | 13 <sub>rms</sub> |      |

| Clock duty cycle                                                           | 4          | Duty cycle                                                                     | 45        | 50       | 55        | %                 |      |

| SYNCTRIG INPUTS                                                            |            |                                                                                |           |          |           |                   |      |

| SYNCTRIG common mode voltage                                               | 1B         | V <sub>ICM</sub>                                                               | 1.125     | 1.25     | 1.8       | V                 |      |

| SYNCTRIG differential swing                                                | 1B         | V <sub>IH</sub> - V <sub>IL</sub>                                              | 100       | 350      | 450       | mVp               |      |

| SYNCTRIG input capacitance                                                 | 5          | C <sub>SYNC</sub>                                                              |           | 1        |           | pf                |      |

| SYNCTRIG input resistance                                                  | 4          | R <sub>SYNC</sub>                                                              | 80        | 100      | 120       | Ω                 |      |

| SYNCTRIG slew rate                                                         | 5          | SR <sub>SYNC</sub>                                                             | 500       |          |           | MV/s              |      |

Teledyne-e2v Semiconductors SAS 2019

|                | Parameter                    | Test  | Gunchal                           |                      | Value | _                   | 11   | Note |

|----------------|------------------------------|-------|-----------------------------------|----------------------|-------|---------------------|------|------|

|                | Parameter                    | level | Symbol                            | Min                  | Тур   | Max                 | Unit | Note |

| SPI INPUTS (RS | TN, SCLK, CSN, MOSI)         |       |                                   |                      |       |                     |      |      |

| CMOS Schmitt   | trigger low level threshold  | 1C    | V <sub>IL</sub>                   |                      |       | 0.3V <sub>CCD</sub> | V    |      |

| CMOS Schmitt   | trigger high level threshold | 1C    | V <sub>IH</sub>                   | $0.6V_{CCD}$         |       |                     | V    |      |

| CMOS Schmitt   | trigger hysteresis           | 5     | $V_{th}$                          | $0.1 V_{\text{CCD}}$ |       |                     | v    |      |

| CMOS low leve  | l input current              | 5     | I <sub>IL</sub>                   |                      |       | 300                 | nA   |      |

| CMOS high leve | el input current             | 5     | I <sub>IH</sub>                   |                      |       | 1000                | nA   |      |

| SPI OUTPUT (N  | 1ISO)                        |       |                                   |                      |       |                     |      |      |

| CMOS low leve  | l output voltage             | 1C    | V <sub>OL</sub>                   |                      |       | $0.2V_{CCD}$        | V    |      |

| CMOS high leve | el output voltage            | 1C    | V <sub>OH</sub>                   | $0.8V_{CCD}$         |       |                     | V    |      |

| LVDS OUTPUT    |                              |       |                                   |                      |       |                     |      |      |

| Full swing     | - Common mode voltage        |       | VO <sub>CM</sub>                  | 1.2                  | 1.36  | 1.55                | V    |      |

|                | - Swing                      |       | V <sub>OH</sub> - V <sub>OL</sub> | 230                  | 320   | 480                 | mVp  |      |

|                | - Logic low                  | 4     | V <sub>OL</sub>                   |                      |       | 1.30                | v    | (7)  |

|                | - Logic high                 |       | V <sub>OH</sub>                   | 1.40                 |       |                     | v    |      |

| Reduced swing  | - Common mode voltage        |       | VO <sub>CM</sub>                  | 1.2                  | 1.36  | 1.55                | V    |      |

|                | - Swing                      |       | V <sub>OH</sub> - V <sub>OL</sub> | 200                  | 290   | 350                 | mVp  |      |

|                | - Logic low                  | 1B    | V <sub>OL</sub>                   |                      |       | 1.40                | V    |      |

|                | - Logic high                 |       | V <sub>OH</sub>                   | 1.35                 |       |                     | V    |      |

Notes: 1. Refer to Table 18 in section <u>DEMUX 1:1 or 1:2</u> for more information on power supplies management.

2. Enabling SDA increases power consumption by 80mW (23mA on VCCA).

3. The DC analog common mode voltage is provided by the CMIREF output of the ADC.

4. See section Input common mode trimming for more information on the range available.

5. For optimal performance, in terms of VSWR, the input impedance must be  $100\Omega \pm 5\%$  and the analog input impedance must be digitally trimmed to cope with process deviation. Refer to section <u>Input impedance trimming</u> for more information.

6. Refer to Figure 21 in section <u>Characterization results</u> for more results on the crosstalk performance.

7. The full swing mode will increase respectively Icco1 by 50mA in DMUX1:1 and by 80mA in DMUX1:2.

### 3.5 Converter characteristics

Unless otherwise specified:

- Values are given for typical supplies in single-rail configuration (Refer to Table 18 in section <u>DEMUX 1:1 or 1:2</u> for more information) at Tamb = +25°C; Value between brackets represents value versus temperature.

- Values are given with SDA disabled and reduced swing mode.

- Sampling frequency (Fs) at 1.5Gsps.

- Both cores comply with the below specification when the OTP have been loaded.

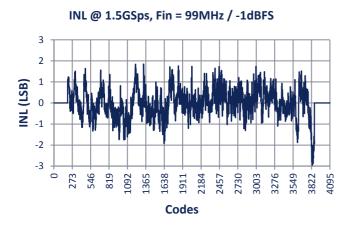

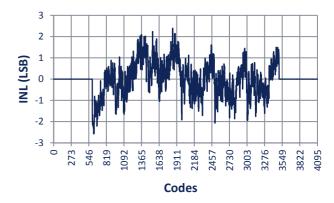

Table 7: Static characteristics

| Devenue ster                                | Test  | Cumple al |      | Value           | _    | 11   | Nata |

|---------------------------------------------|-------|-----------|------|-----------------|------|------|------|

| Parameter                                   | level | Symbol    | Min  | Тур             | Max  | Unit | Note |

| DC accuracy / Fs = 1.5GSps, Fin = 100MHz, - | 1dBFS |           |      |                 |      |      |      |

| Gain variation                              | 5     | Go        | -1.5 | 0               | 1.5  | dB   | (1)  |

| Gain variation versus temperature           | 4     | G(T)      | -0.5 | 0               | 0.5  | dB   |      |

| DC offset                                   | 1B    |           | 2045 | 2048            | 2051 | LSB  | (2)  |

|                                             |       |           |      | No missing code |      |      |      |

| Differential Non Linearity                  | 4     | DNL       | -0.9 |                 | +1.5 | LSB  |      |

| DNL rms                                     | 4     | DNLrms    |      | 0.2             | 0.5  | LSB  |      |

| Integral Non Linearity                      | 1B    | INL       | -6.5 |                 | 6.5  | LSB  |      |

| INL rms                                     | 1B    | INLrms    |      | 0.6             | 1.6  | LSB  |      |

Notes: 1. This value corresponds to the maximum deviation from part to part.

2. Mid code at ADC output after DC offset calibration.

#### Table 8: Dynamic characteristics

| Demonster                                                                                  | Test  | C      |     | Value |        | Unit |      |

|--------------------------------------------------------------------------------------------|-------|--------|-----|-------|--------|------|------|

| Parameter                                                                                  | level | Symbol | Min | Тур   | Max    |      | Note |

| ANALOG INPUT                                                                               |       |        |     |       |        |      |      |

| Full power input bandwidth                                                                 |       |        |     |       |        |      |      |

| Nominal bandwidth (NBW)                                                                    | 4     |        |     | 3.7   |        | GHz  | (1)  |

| • Extended bandwidth (EBW)                                                                 | 4     |        |     | 4.3   |        | GHz  |      |

| Gain flatness (+/- 0.5dB)                                                                  |       |        |     |       |        |      |      |

| Nominal bandwidth (NBW)                                                                    | 4     |        |     | 900   |        | MHz  |      |

| • Extended bandwidth (EBW)                                                                 | 4     |        |     | 1000  |        | MHz  |      |

| Input voltage standing wave ratio                                                          |       |        |     |       |        |      |      |

| • Up to 2.4GHz                                                                             | 4     | VSWR   |     | 1.2:1 | 1.28:1 |      |      |

| • Up to 5GHz                                                                               | 4     |        |     | 2:1   |        |      |      |

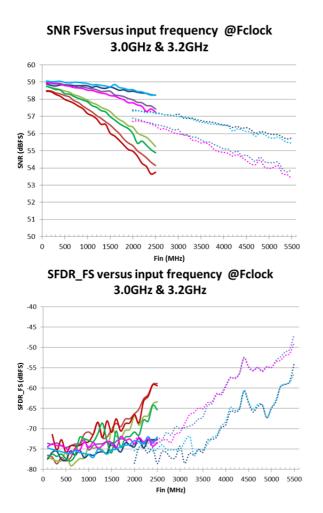

| DYNAMIC PERFORMANCE                                                                        | •     |        |     |       |        |      | •    |

| Noise Power Ratio<br>(600MHz noise bandwidth, 5MHz notch<br>centered at F <sub>s</sub> /4) |       |        |     |       |        |      |      |

| • 1 <sup>st</sup> Nyquist zone                                                             | 4     | NPR    |     | 50    |        | dB   | (2)  |

| • 2 <sup>nd</sup> Nyquist zone                                                             | 4     | NPK    |     | 47    |        | dB   | (2)  |

| • 3 <sup>rd</sup> Nyquist zone                                                             | 4     |        |     | 46    |        | dB   |      |

| • 4 <sup>th</sup> Nyquist zone                                                             | 4     |        |     | 45    |        | dB   |      |

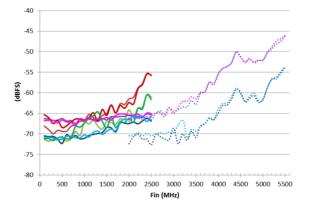

| Spurious Free Dynamic Range                                                                |       |        |     |       |        |      |      |

| Output level -1dBFS                                                                        |       |        |     |       |        |      |      |

| • Fin = 100MHz, NBW                                                                        | 4     | SFDR   |     | 76    |        | dBFS | (3)  |

| Parameter                                  | Test Symbol |        | Value   |                                         |     | Unit | Note |

|--------------------------------------------|-------------|--------|---------|-----------------------------------------|-----|------|------|

| Parameter                                  | level       | Symbol | Min     | Тур                                     | Max | onit | Note |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 70                                      |     | dBFS | Ī    |

| • Fin = 1900MHz, NBW                       | 4           |        |         | 68                                      |     | dBFS |      |

| Output level -3dBFS                        |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 77                                      |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 70                                      |     | dBFS |      |

| • Fin = 1900MHz, NBW                       | 4           |        |         | 69                                      |     | dBFS |      |

| Output level -8dBFS                        |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 74                                      |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 74                                      |     | dBFS |      |

| • Fin = 1900MHz, NBW                       | 1B          |        | 69 (66) | 75 (73)                                 |     | dBFS |      |

| • Fin = 2980MHz, EBW                       | 1B          |        | 64 (63) | 73 (68)                                 |     | dBFS | (3)  |

| • Fin = 3730MHz, EBW                       | 4           | SFDR   |         | 62                                      |     | dBFS |      |

| • Fin = 5300MHz, out-of-band               | 4           |        |         | 51                                      |     | dBFS |      |

| Output level -12dBFS                       |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 77.5                                    |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 74                                      |     | dBFS |      |

| • Fin = 1900MHz, NBW                       | 1B          |        | 66 (64) | 76 (72)                                 |     | dBFS |      |

| • Fin = 2980MHz, EBW                       | 1B          |        | 67 (63) | 77 (71)                                 |     | dBFS |      |

| • Fin = 3730MHz, EBW                       | 4           |        |         | 68                                      |     | dBc  |      |

| • Fin = 5300MHz, out-of-band               | 4           |        |         | 59                                      |     | dBFS |      |

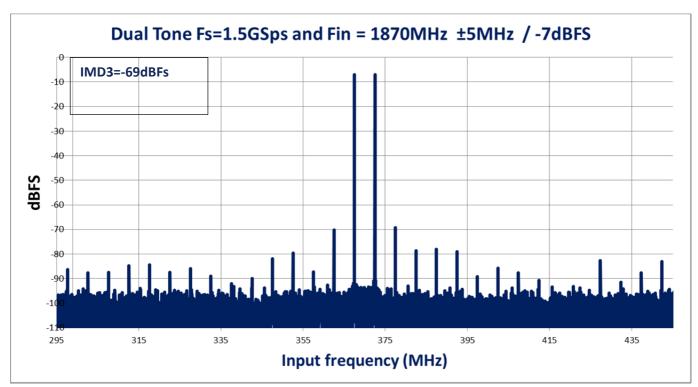

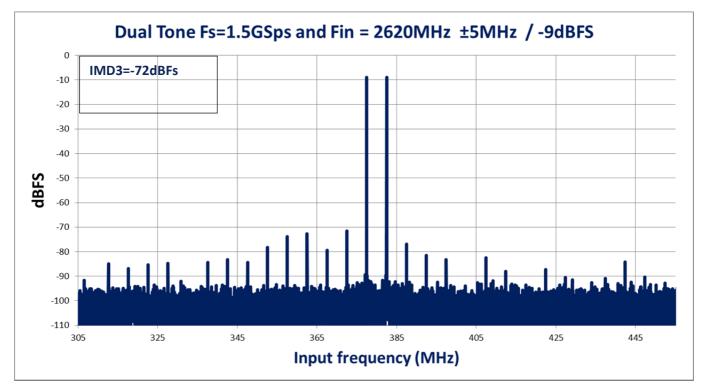

| 3rd order highest intermodulation products |             | IMD3   |         |                                         |     |      | (3)  |

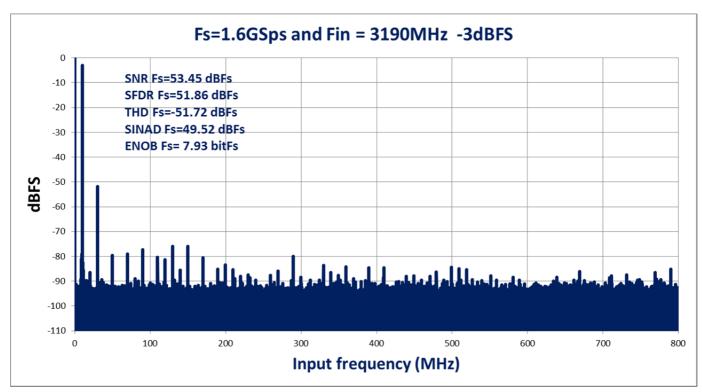

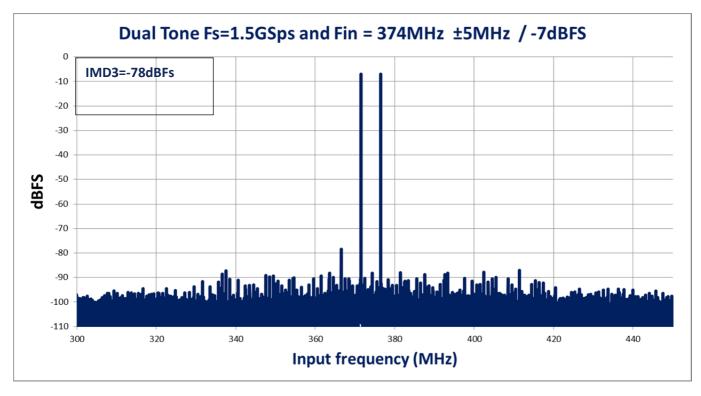

| Fin = 374MHz & ΔFin = 5MHz / -7dBFS        | 4           |        |         | 78.5                                    |     | dBFS |      |

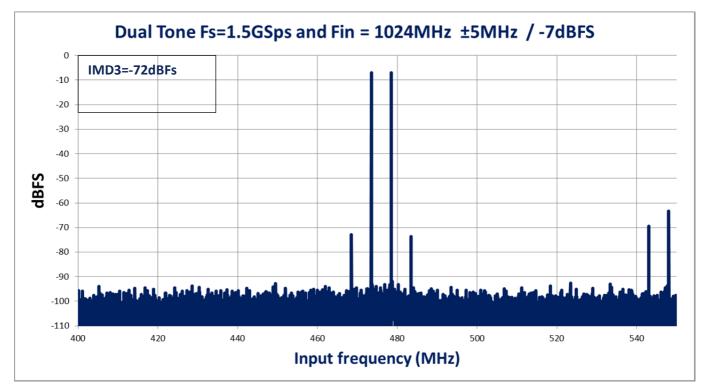

| Fin = 1024MHz & ΔFin = 5MHz / -7dBFS       | 4           |        |         | 72.7                                    |     | dBFS |      |

| Fin = 1870MHz & ΔFin = 5MHz / -7dBFS       | 4           |        |         | 69.2                                    |     | dBFS |      |

| Fin = 2620MHz & ΔFin = 5MHz / -9dBFS       | 4           |        |         | 71.6                                    |     | dBFS |      |

|                                            |             |        |         |                                         |     |      |      |

| Total Harmonic Distortion                  |             |        |         |                                         |     |      |      |

| Output level -1dBFS                        |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 68                                      |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 65                                      |     | dBFS |      |

| Output level -3dBFS                        |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 71                                      |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           |        |         | 67                                      |     | dBFS |      |

| Output level -8dBFS                        |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 69                                      |     | dBFS |      |

| • Fin = 1480MHz, NBW                       | 4           | THD    |         | 69                                      |     | dBFS | (3)  |

| • Fin = 1900MHz, NBW                       | 1B          |        | 63 (61) | 69 (67)                                 |     | dBFS |      |

| • Fin = 2980MHz, EBW                       | 1B          |        | 62 (58) | 68 (63)                                 |     | dBFS |      |

| • Fin = 3730MHz, EBW                       | 4           |        |         | 60                                      |     | dBFS |      |

| • Fin = 5300MHz, out-of-band               | 4           |        |         | 48                                      |     | dBFS |      |

| Output level -12dBFS                       |             |        |         |                                         |     |      |      |

| • Fin = 100MHz, NBW                        | 4           |        |         | 71                                      |     | dBFS |      |

| <ul> <li>Fin = 1480MHz, NBW</li> </ul>     | 4           |        |         | 70                                      |     | dBFS |      |

| <ul> <li>Fin = 1900MHz, NBW</li> </ul>     | -<br>1B     |        | 62 (59) | 70 (66)                                 |     | dBFS |      |

| <ul> <li>Fin = 2980MHz, EBW</li> </ul>     | 1B<br>1B    |        | 62 (60) | 70 (66)                                 |     | dBFS |      |

| - THI - 250010112, LDVV                    | 10          |        | 02 (00) | , , , , , , , , , , , , , , , , , , , , |     |      | I    |

|                                | Test  |        | Value       |           |     | 110.14 |      |

|--------------------------------|-------|--------|-------------|-----------|-----|--------|------|

| Parameter                      | level | Symbol | Min         | Тур       | Max | Unit   | Note |

| • Fin = 3730MHz, EBW           | 4     | •      |             | 65        |     | dBFS   |      |

| • Fin = 5300MHz, out-of-band   | 4     |        |             | 55        |     | dBFS   |      |

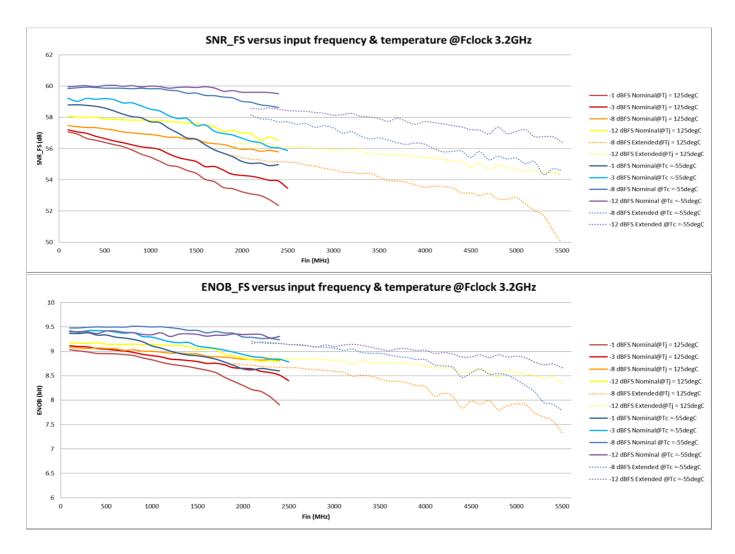

| Signal to Noise Ratio          |       |        |             |           |     |        |      |

| Output level -1dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     | SNR    |             | 58        |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 56.5      |     | dBFS   |      |

| Output level -3dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 58.5      |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 57.5      |     | dBFS   |      |

| Output level -8dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 59        |     |        |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 58.5      |     |        |      |

| • Fin = 1900MHz, NBW           | 1B    |        | 57 (55)     | 58 (57)   |     |        |      |

| • Fin = 2980MHz, EBW           | 1B    |        | 54.5 (53.5) | 56 (55.5) |     |        |      |

| • Fin = 3730MHz, EBW           | 4     | SNR    |             | 55.5      |     |        |      |

| • Fin = 5300MHz, out-of-band   | 4     |        |             | 54        |     |        |      |

| Output level -12dBFS           |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 59        |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 59        |     | dBFS   |      |

| • Fin = 1900MHz, NBW           | 1B    |        | 57 (55.5)   | 59 (57.5) |     | dBFS   |      |

| • Fin = 2980MHz, EBW           | 1B    |        | 55.5 (54)   | 57 (56.5) |     | dBFS   |      |

| • Fin = 3730MHz, EBW           | 4     |        |             | 56        |     | dBFS   |      |

| • Fin = 5300MHz, out-of-band   | 4     |        |             | 55        |     | dBFS   |      |

| Signal to Noise And Distortion |       |        |             |           |     |        |      |

| Output level -1dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 58        |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 56        |     | dBFS   |      |

| Output level -3dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 58.5      |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 56.5      |     | dBFS   |      |

| Output level -8dBFS            |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 58.5      |     |        |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 58        |     |        |      |

| • Fin = 1900MHz, NBW           | 1B    | SINAD  | 56 (54)     | 58 (56.5) |     |        |      |

| • Fin = 2980MHz, EBW           | 1B    |        | 54 (51)     | 56 (54)   |     |        |      |

| • Fin = 3730MHz, EBW           | 4     |        |             | 55        |     |        |      |

| • Fin = 5300MHz, out-of-band   | 4     |        |             | 49        |     |        |      |

| Output level -12dBFS           |       |        |             |           |     |        |      |

| • Fin = 100MHz, NBW            | 4     |        |             | 58.5      |     | dBFS   |      |

| • Fin = 1480MHz, NBW           | 4     |        |             | 58.5      |     | dBFS   |      |

| • Fin = 1900MHz, NBW           | 1B    |        | 56.5 (54)   | 58.5 (57) |     | dBFS   |      |

| • Fin = 2980MHz, EBW           | 1B    |        | 55 (53)     | 57 (55.5) |     | dBFS   |      |

| • Fin = 3730MHz, EBW           | 4     |        |             | 56        |     | dBFS   |      |

| • Fin = 5300MHz, out-of-band   | 4     |        |             | 54        |     | dBFS   |      |

Dual channel 12 bits 1.6GSps ADC

| Demonster                           | Test  | Currents and |           | Value     | _   |        | Nete |

|-------------------------------------|-------|--------------|-----------|-----------|-----|--------|------|

| Parameter                           | level | Symbol       | Min       | Тур       | Max | Unit   | Note |

| Effective Number Of Bits            |       |              |           |           |     |        |      |

| Output level -1dBFS                 |       |              |           |           |     |        |      |

| • Fin = 100MHz, NBW                 | 4     |              |           | 9.4       |     | bit FS |      |

| • Fin = 1480MHz, NBW                | 4     |              |           | 9.0       |     | bit FS |      |

| Output level -3dBFS                 |       |              |           |           |     |        |      |

| • Fin = 100MHz, NBW                 | 4     |              |           | 9.4       |     | bit FS |      |

| • Fin = 1480MHz, NBW                | 4     |              |           | 9.2       |     | bit FS |      |

| Output level -8dBFS                 |       |              |           |           |     |        |      |

| • Fin = 100MHz, NBW                 | 4     |              |           | 9.5       |     | bit FS |      |

| • Fin = 1480MHz, NBW                | 4     | ENOB         |           | 9.4       |     | bit FS |      |

| • Fin = 1900MHz, NBW                | 1B    |              | 9 (8.8)   | 9.3 (9.1) |     | bit FS |      |

| • Fin = 2980MHz, EBW                | 1B    |              | 8.8 (8.4) | 9.0 (8.7) |     | bit FS |      |

| • Fin = 3730MHz, EBW                | 4     |              |           | 8.5       |     | bit FS |      |

| • Fin = 5300MHz, out-of-band        | 4     |              |           | 7.5       |     | bit FS |      |

| Output level -12dBFS                |       |              |           |           |     |        |      |

| • Fin = 100MHz, NBW                 | 4     |              |           | 9.5       |     | bit FS |      |

| • Fin = 1480MHz, NBW                | 4     |              |           | 9.5       |     | bit FS |      |

| • Fin = 1900MHz, NBW                | 1B    |              | 9.1 (8.7) | 9.4 (9.2) |     | bit FS |      |

| • Fin = 2980MHz, EBW                | 1B    |              | 9 (8.6)   | 9.2 (9.0) |     | bit FS |      |

| • Fin = 3730MHz, EBW                | 4     |              |           | 9.0       |     | bit FS |      |

| • Fin = 5300MHz, out-of-band        | 4     |              |           | 8.5       |     | bit FS |      |

| Noise Spectral density at -1dBFS    |       |              |           |           |     |        |      |

| • 1 <sup>st</sup> Nyquist zone, NBW | 4     |              |           | -147      |     | dBm/Hz |      |

| • 2 <sup>nd</sup> Nyquist zone, NBW | 4     |              |           | -145      |     | dBm/Hz |      |

| • 3 <sup>rd</sup> Nyquist zone, EBW | 4     |              |           | -144      |     | dBm/Hz |      |

| • 4 <sup>th</sup> Nyquist zone, EBW | 4     | NCD          |           | -141      |     | dBm/Hz |      |

| Noise Spectral density at -8dBFS    |       | NSD          |           |           |     |        |      |

| • 1 <sup>st</sup> Nyquist zone, NBW | 4     |              |           | -147      |     | dBm/Hz |      |

| • 2 <sup>nd</sup> Nyquist zone, NBW | 4     |              |           | -146      |     | dBm/Hz |      |

| • 3 <sup>rd</sup> Nyquist zone, EBW | 4     |              |           | -146      |     | dBm/Hz |      |

| • 4 <sup>th</sup> Nyquist zone, EBW | 4     |              |           | -144      |     | dBm/Hz |      |

Notes: 1. Optimal bandwidth selection depends on signal characteristic; the bandwidth selection allows optimizing noise and linearity trade-off. For signal below 2.0GHz, the bandwidth selection must be set to nominal, for large signal beyond 2GHz the bandwidth selection must be set to extended. The extended bandwidth degrades noise floor up to 1dB, but brings lower signal attenuation with high frequency input.

2. The values indicated in this table indicate the NPR value obtained at optimum loading factor value.

3. Linearity at high frequency is dominated by low order odd harmonics (especially H3). Phase difference on the differential inputs should be reduced as much as possible to optimize the 2<sup>nd</sup> harmonic (H2) level. Stepping back 3 or 6 dB on input signal gives significant improvement on SFDR figures.

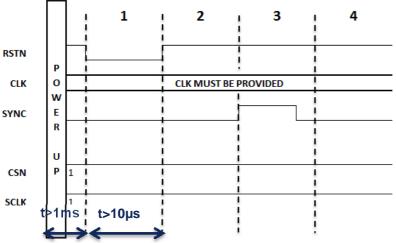

### 3.6 Transient and switching characteristics

Unless otherwise specified:

- Typical values are given for typical supplies in dual-rail configuration (Refer to Table 18 in section <u>DEMUX 1:1 or 1:2</u> for more information) at Tamb = +25°C.

- Both cores comply with the below specification when the OTP have been loaded.

- Values are specified at Fs = 1.5GSps.

- Values are given with SDA disabled.

### Table 9: Transient characteristics

| Demonster                                     | Test  | Gunahal |     | _                 | 11  | Nata |      |

|-----------------------------------------------|-------|---------|-----|-------------------|-----|------|------|

| Parameter                                     | level | Symbol  | Min | Тур               | Max | Unit | Note |

| ADC Code Error Rate at 1.5 GSps (3GHz CLK)    | 4     | CER     |     | 10 <sup>-12</sup> |     |      | (1)  |

| ADC Code error rate at 1.25 GSps (2.5GHz CLK) | 4     | CER     |     | 10 <sup>-15</sup> |     |      | (2)  |

| Overvoltage Recovery Time                     | 4     | ORT     |     | 666               |     | ps   |      |

Notes: 1. Output error amplitude > 128 LSB (3% of the full-scale). At Fs = 1.5 GSps, ambient temperature.

2. Output error amplitude > 64 LSB (1.5% of the full-scale). At Fs = 1.25 GSps, ambient temperature.

### Table 10: Switching characteristics

| <b>-</b> .                                               | Test  |                   |     | Value   |       |                  |          |  |

|----------------------------------------------------------|-------|-------------------|-----|---------|-------|------------------|----------|--|

| Parameter                                                | level | Symbol            | Min | Min Typ |       | Unit             | Note     |  |

| External clock frequency                                 | 4     | F <sub>CLK</sub>  | 400 |         | 3200  | MHz              |          |  |

| Sampling frequency for performance                       |       |                   |     |         |       |                  |          |  |

| • DEMUX 1:1                                              | 4     | F <sub>S1:1</sub> | 200 |         | 1500  | MSps             | (1)      |  |

| • DEMUX 1:2                                              |       | F <sub>S1:2</sub> | 200 |         | 1600  | MSps             |          |  |

| Sampling frequency for operation                         |       |                   |     |         |       |                  |          |  |

| • DEMUX 1:1                                              | 4     | F <sub>S1:1</sub> | 200 |         | 1500  | MSps             | (1)      |  |

| • DEMUX 1:2                                              | 4     | F <sub>S1:2</sub> | 200 |         | 1600  | MSps             |          |  |

| Aperture delay (SDA disabled)                            | 4     | T <sub>A</sub>    |     | 135     |       | ps               |          |  |

| Aperture delay tuning range (SDA enabled)                | 4     | T <sub>A</sub>    | 120 | 175     |       | ps               |          |  |

| LVDS OUTPUT                                              |       |                   |     | •       |       |                  |          |  |

| Rise time for data (20-80%)                              | 4     | T <sub>R</sub>    |     | 165     |       | ps               | (1), (2) |  |

| Fall time for data (20-80%)                              | 4     | Τ <sub>F</sub>    |     | 165     |       | ps               | (1), (2) |  |

| Rise time for data ready (20-80%)                        | 4     | T <sub>R</sub>    |     | 135     |       | ps               | (1), (2) |  |

| Fall time for data ready (20-80%)                        | 4     | T <sub>F</sub>    |     | 135     |       | ps               | (1), (2) |  |

| Output data pipeline delay (latency)                     |       |                   |     |         |       |                  |          |  |

| • Port high                                              | 4     | T <sub>PDH</sub>  |     | 22      |       | T <sub>CLK</sub> | (3)      |  |

| Port low                                                 | 4     | T <sub>PDL</sub>  |     | 20      |       | T <sub>CLK</sub> |          |  |

| Output data propagation delay                            | 4     | T <sub>OD</sub>   |     | 2.5     |       | ns               | (3)      |  |

| Output data to data ready delay in<br>DMUX1:1<br>DMUX1:2 | 4     | T <sub>D1</sub>   |     | 1 2     |       | Т <sub>сік</sub> | (3)      |  |

| Output data ready to data delay in<br>DMUX1:1<br>DMUX1:2 | 4     | T <sub>D2</sub>   |     | 1 2     |       | T <sub>CLK</sub> | (3)      |  |

| Output data ready A to data ready B skew                 | 4     | T <sub>DRsk</sub> |     | 43      |       | ps               |          |  |

| Output data skew within 1 port reference to dataready    | 4     | Tdxsk             | -23 |         | +14.5 |                  |          |  |

| SYNC to data ready pipeline delay                        | 4     |                   |     |         |       |                  |          |  |

| Devenueter                      | Test  | Gumbal                           |     | Value      | -   | Unit             | Note |  |

|---------------------------------|-------|----------------------------------|-----|------------|-----|------------------|------|--|

| Parameter                       | level | Symbol                           | Min | Тур        | Max | Unit             |      |  |

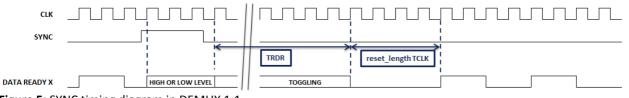

| • DEMUX 1:1                     | 4     | T <sub>RDR</sub>                 |     | 26         |     | T <sub>CLK</sub> | (4)  |  |

| • DEMUX 1:2                     | 4     | T <sub>RDR</sub>                 |     | 27         |     | T <sub>CLK</sub> |      |  |

| SYNC pulse width                | 4     | T <sub>SYNC</sub>                | 16  |            |     | T <sub>CLK</sub> |      |  |

| SYNC to SYNCO pipeline delay    | 4     | T <sub>PS</sub>                  |     | 1          |     | T <sub>CLK</sub> |      |  |

| SYNC to SYNCO propagation delay | 4     | T <sub>ODS</sub>                 |     | 1          |     | ns               |      |  |

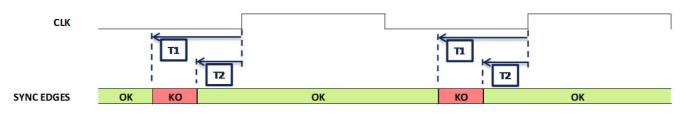

| SYNC signal valid timing        | 4     | T <sub>1</sub><br>T <sub>2</sub> |     | 140<br>125 |     | ps<br>ps         | (5)  |  |

| Trigger data pipeline delay     |       |                                  |     |            |     |                  |      |  |

| Core A high                     | 4     | T <sub>PDA</sub>                 |     | 22         |     | T <sub>CLK</sub> | (6)  |  |

| • Core B                        |       | T <sub>PDB</sub>                 |     | 23         |     | T <sub>CLK</sub> |      |  |

| TRIG propagation delay          | 4     | T <sub>ODT</sub>                 |     | 4.34       |     | ns               |      |  |

Notes: 1. Performance only guaranteed at 1.5 GSps max in DEMUX 1:2 mode and 1.3 GSps max in DEMUX 1:1 mode although devices still exhibit very good performance at 1.6Gsps.

2. Simulated with  $50\Omega$  lines modeled by 2.5nH in parallel with 1pF.

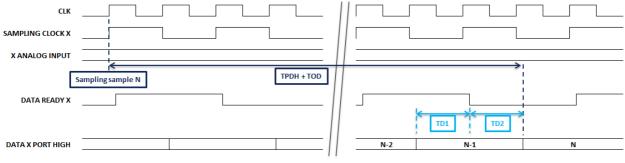

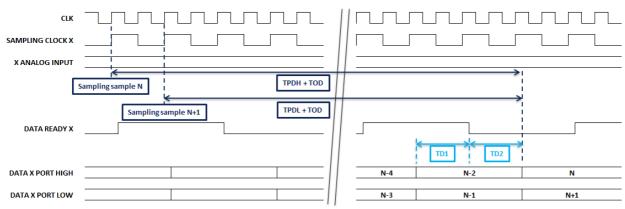

3. Refer to timing diagrams in Figure 3 and 4.

4. Refer to timing diagram in Figure 5.

5. Refer to timing diagram in Figure 6. T1 and T2 correspond to setup and hold times of the SYNCTRIG input seen at the package input.

6. Measured in interleaved mode.

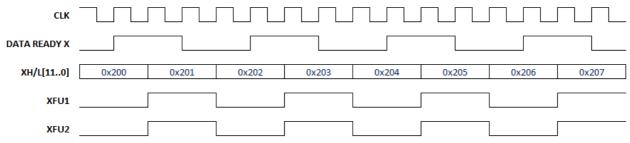

Figure 4: Timing diagram in DEMUX 1:2

For both figures 3 and 4, X represents either channel A or B. If channel A and B are interleaved, the internal sampling clocks of channel A and B are in opposition and their output data and data ready are delayed by 1 external CLK cycle.

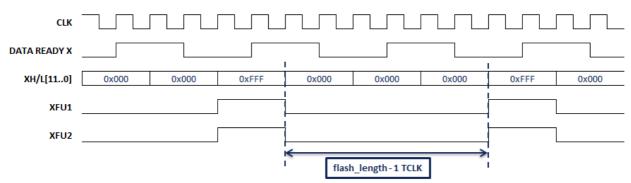

Figure 5: SYNC timing diagram in DEMUX 1:1

Notes: In DEMUX 1:2 the only difference from the timing diagram above is the frequency of the data ready.

Figure 6: SYNC edges forbidden zone

Notes: The timing diagram assumes that bit ESEL in register SYNC control is at '0'. If ESEL = '1', T1 and T2 have to be referenced to the falling edge of CLK. See section <u>SYNCTRIG input</u> for more information.

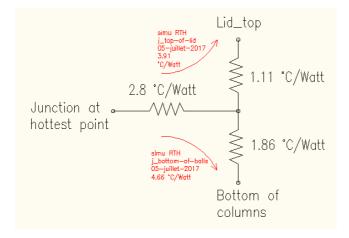

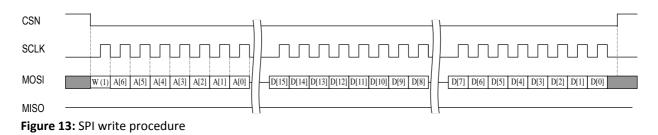

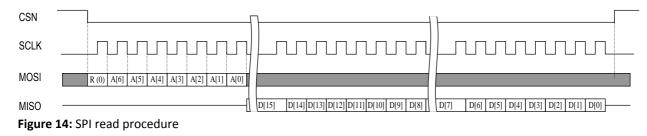

Table 11: SPI switching characteristics

| Parameter         | Test  | Symbol                |     |         | Unit | Note              |         |

|-------------------|-------|-----------------------|-----|---------|------|-------------------|---------|

| - didineter       | level | Symbol                | Min | Min Typ |      | onic              | Note    |

| RSTN pulse length | 5     | T <sub>RSTN</sub>     | 10  |         |      | μs                |         |

| SCLK frequency    | 5     | F <sub>SCLK</sub>     |     |         | 30   | MHz               |         |

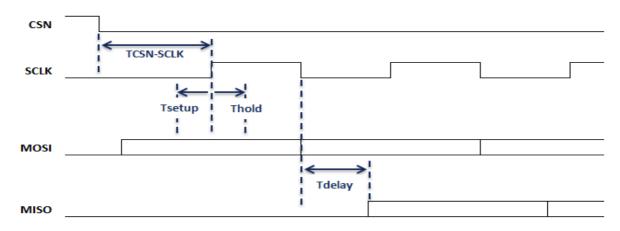

| CSN to SCLK delay | 5     | T <sub>CSN-SCLK</sub> | 0.5 |         |      | T <sub>SCLK</sub> | (1)     |

| MOSI setup time   | 5     | T <sub>setup</sub>    | 3   |         |      | ns                | (1,2)   |

| MOSI hold time    | 5     | T <sub>hold</sub>     | 3   |         |      | ns                | (1,2)   |

| MISO output delay |       | $T_{delay}$           |     |         | 4    | ns                | (1,2,3) |

Notes:

- 1. Refer to timing diagram in Figure 7.

- 2. ADC is considered as the slave.

- 3. Taking into account 5pF as load.

Figure 7: SPI timing diagram

### 3.7 Digital output coding

| Table 12: ADC digital output coding table | Table | 12: / | ٩DC | digital | output | coding table |

|-------------------------------------------|-------|-------|-----|---------|--------|--------------|

|-------------------------------------------|-------|-------|-----|---------|--------|--------------|

| Differential analog<br>input | Voltage level                | Binary<br>MSB (bit 11)LSB(bit 0) In-range |

|------------------------------|------------------------------|-------------------------------------------|

| > +499.756 mV                | > Top end of full scale      | 1111 1111 1111 0                          |

| +499.756 mV                  | Top end of full scale        | 1111 1111 1111 1                          |

| +499.512 mV                  | Top end of full scale -1 LSB | 1111 1111 1110 1                          |

| 0 mV                         | Mid-scale                    | 1000 0000 0000 1                          |

| -0.244 mV                    | Mid-scale – 1 LSB            | 0111 1111 1111 1                          |

| -499.756 mV                  | Bottom of full scale + 1 LSB | 0000 0000 0001 1                          |

| -500 mV                      | Bottom of full scale         | 0000 0000 0000 1                          |

| < -500 mV                    | < Bottom of full scale       | 0000 0000 0000 0                          |

### 3.8 Characterized radiation level

| TID | 150Krad(SI) at Low Dose Rate (36rad(Si)/h, 10mrad(Si)/s)               |

|-----|------------------------------------------------------------------------|

| SEE | SEL and SEFI immune up to a LET of 80MeV.cm <sup>2</sup> /mg (No tilt) |

### 3.9 Definition of terms

### Table 13: Definition of terms

| Abbreviation | Term                          | Definition                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|--------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| CER          | Code Error Rate               | Probability to exceed a specified error threshold for a sample at maximum specified sampling rate.                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| DNL          | Differential non-linearity    | step size of code "i" and the ideal LSB step size. DNI value of all DNL (i). DNL error specification highe                                                                                                                                                           | he Differential Non Linearity for an output code "i" is the difference between the measured<br>rep size of code "i" and the ideal LSB step size. DNL (i) is expressed in LSBs. DNL is the maximum<br>alue of all DNL (i). DNL error specification higher than -1 LSB guarantees that there are no<br>hissing output codes and that the transfer function is monotonic. |  |  |  |  |  |  |  |

| ENOB         | Effective Number Of Bits      | ENOB =                                                                                                                                                                                                                                                               | Where A is the input amplitude and FS is the full scale range of the ADC under test.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| FPBW         | Full Power Input<br>Bandwidth | nalog input frequency at which the fundamental component in the digitally reconstructed utput waveform has fallen by 3 dB with respect to its low frequency value (determined by FFT nalysis) for input at -1dBFS (Full scale – 1dB).                                |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| IMD3         | Intermodulation<br>Distortion | The two tones intermodulation distortion (IMD) rejection is the ratio of either input tone to the worst third order intermodulation products. It may be reported in dBFS (i.e., related to converter full scale), or in dBc (i.e., related to carrier signal level). |                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| INL          | Integral non-linearity        | The Integral Non Linearity for an output code "i" is<br>voltage at which the transition occurs an<br>INL (i) is expressed in LSBs, and is the maximum valu                                                                                                           | d the ideal value of this transition.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| JITTER       | Aperture uncertainty          | Sample to sample variation in aperture delay. The slew rate of the signal at the sampling point.                                                                                                                                                                     | voltage error due to jitter depends on the                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| LF           | Loading Factor                |                                                                                                                                                                                                                                                                      | The loading factor is 20log(1/k), where k is the rms value of the broadband signal. This parameter relates to the NPR measurement. The optimum loading factor for a 12bits converter                                                                                                                                                                                   |  |  |  |  |  |  |  |

| NPR          | Noise Power Ratio             | The NPR is measured to characterize the ADC pe<br>signals. When applying a notch-filtered broadbanc                                                                                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Abbreviation | Term                                    | Definition                                                                                                                                                                                                                                                                                                                 |

|--------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|